Что есть System Clock

Вт окт 31, 2023 08:26:14

(STM32G0)

В RM часто фигурирует понятие System clock.

Например "...чтобы использовать режим Low Power Run, частота System Clock не должна превышать 2 МГц" ("Low-power run mode: This mode is achieved when the system clock frequency is reduced below 2 MHz.")

При этом непонятно, какая конкретно из частот имеется в виду.

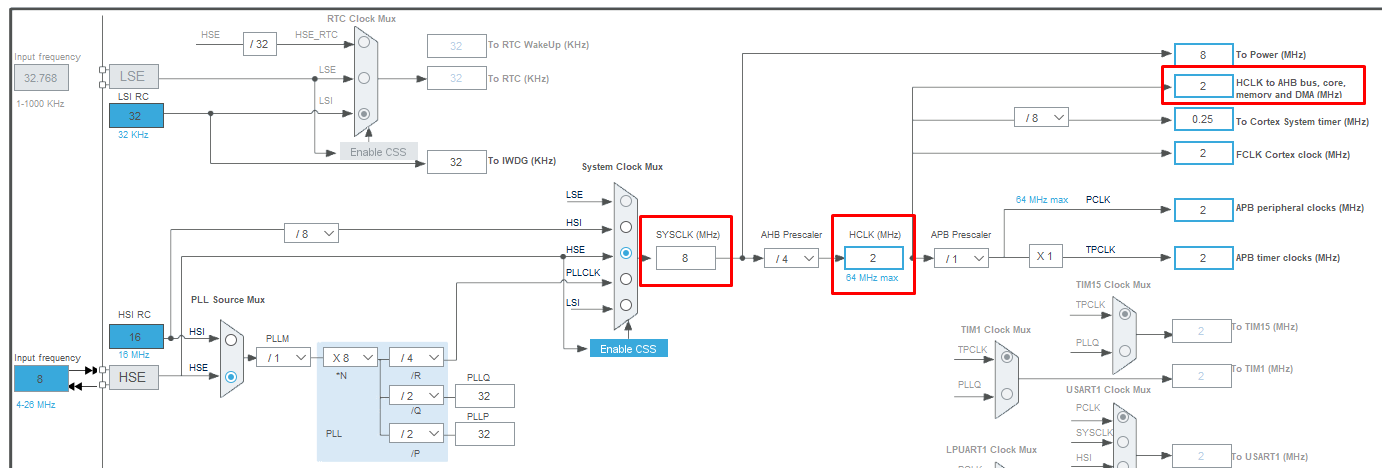

Например, на дереве тактирования есть частота SYSCLK, которая получается на выходе System Clock Mux.

Дальше SYSCLK непосредственно идет только на модуль PWR, в остальном же она идет на делитель HCLK, от которого уже именно частота HCLK идет на ядро, память и всё остальное.

Не пойму, какую из частот нужно сделать 2 МГц, чтобы исползовать режим LP Run (SYSCLK или HCLK). Если это частота SYSCLK, то непонятно, как ее получить 2 МГц, и продолжать при этом использовать внешний кварц (делителей HSE до SYSCLK не предусмотрено, сам кварц д.б. частотой 4 МГц и более).

Если в RM имеется в виду всё-таки HCLK, то почему она в RM обозвана System Clock, когда по логике названия System Clock это именно SYSCLK.

В RM часто фигурирует понятие System clock.

Например "...чтобы использовать режим Low Power Run, частота System Clock не должна превышать 2 МГц" ("Low-power run mode: This mode is achieved when the system clock frequency is reduced below 2 MHz.")

При этом непонятно, какая конкретно из частот имеется в виду.

Например, на дереве тактирования есть частота SYSCLK, которая получается на выходе System Clock Mux.

Дальше SYSCLK непосредственно идет только на модуль PWR, в остальном же она идет на делитель HCLK, от которого уже именно частота HCLK идет на ядро, память и всё остальное.

Не пойму, какую из частот нужно сделать 2 МГц, чтобы исползовать режим LP Run (SYSCLK или HCLK). Если это частота SYSCLK, то непонятно, как ее получить 2 МГц, и продолжать при этом использовать внешний кварц (делителей HSE до SYSCLK не предусмотрено, сам кварц д.б. частотой 4 МГц и более).

Если в RM имеется в виду всё-таки HCLK, то почему она в RM обозвана System Clock, когда по логике названия System Clock это именно SYSCLK.

- Вложения

-

- Clocks.png

- (49.18 KiB) Скачиваний: 248

Re: Что есть System Clock

Вт окт 31, 2023 16:34:10

Дальше SYSCLK непосредственно идет только на модуль PWR

....

Не пойму, какую из частот нужно сделать 2 МГц, чтобы исползовать режим LP Run

....

Не пойму, какую из частот нужно сделать 2 МГц, чтобы исползовать режим LP Run

Re: Что есть System Clock

Вт окт 31, 2023 17:05:01

Иными словами, LPRun и внешний кварц - вещи несовместимые, печально.

Re: Что есть System Clock

Вт окт 31, 2023 17:18:34

тогда печально, что на малом потреблении невозможно и всё остальное

Добавлено after 9 minutes 47 seconds:

и что-то мне не верится, что в PLL невозможно наделить.

Добавлено after 2 minutes 10 seconds:

ну да. один только PLLM может до 8 поделить

Добавлено after 9 minutes 47 seconds:

и что-то мне не верится, что в PLL невозможно наделить.

Добавлено after 2 minutes 10 seconds:

ну да. один только PLLM может до 8 поделить

Re: Что есть System Clock

Вт окт 31, 2023 17:20:19

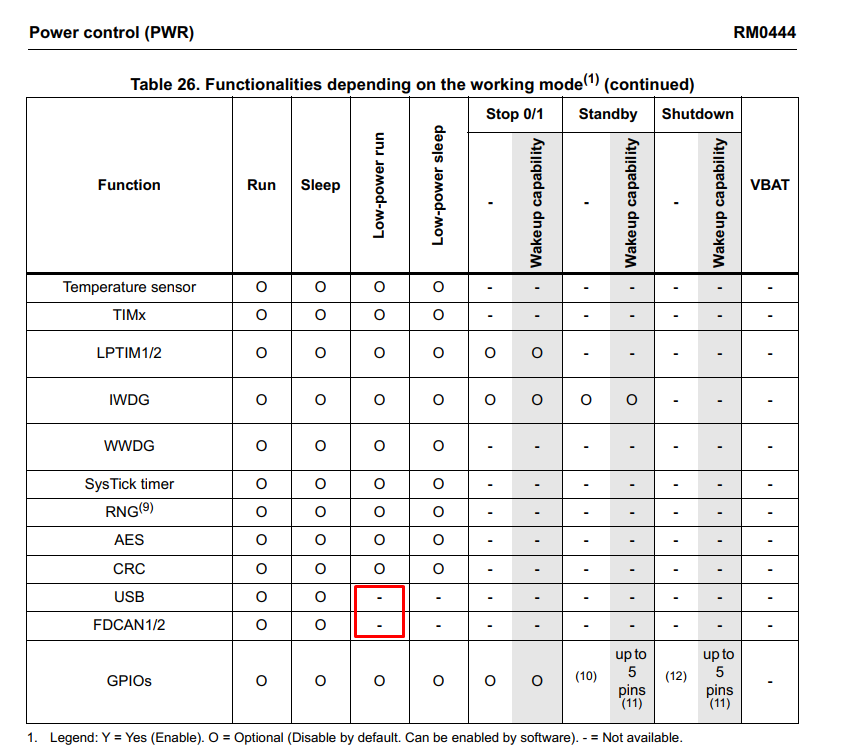

В том то и дело, что не всё недоступно. Но вот что конкретно доступно, а что нет - разобраться порой сложно, даташит и RM полны противоречий как с практикой, так и друг с другом (например, тяжелая периферия, которая судя по даташиту недоступна в LP-run, по факту в нём у меня работает).

PS: А вот PLL в LP-run сам по себе недоступен.

PS: А вот PLL в LP-run сам по себе недоступен.

Re: Что есть System Clock

Вт окт 31, 2023 18:22:53

что-то не увидел описания этого, что PLL недоступен. Но я наспех проглядел.

Противоречия и ошибки там бывают, эт да. Но крайне редко. По себе я замечал, что если мне кажется, что есть противоречие, то либо я неверно понял, перевёл или что-то не дочитал.

Так что, если что-то не должно работать, но работает, то высока вероятность, что этот режим не установился или что оно и должно работать.

Добавлено after 5 minutes 48 seconds:

Поглядел по stm32g030 - всё там работает... для всей периферии указано потребление при LP Run

PLL да, работать не будет, у неё минимальный выход 3.09 МГц, что противоречит условию. То есть, с её помощью режим LP Run не получить.

Противоречия и ошибки там бывают, эт да. Но крайне редко. По себе я замечал, что если мне кажется, что есть противоречие, то либо я неверно понял, перевёл или что-то не дочитал.

Так что, если что-то не должно работать, но работает, то высока вероятность, что этот режим не установился или что оно и должно работать.

Добавлено after 5 minutes 48 seconds:

Поглядел по stm32g030 - всё там работает... для всей периферии указано потребление при LP Run

PLL да, работать не будет, у неё минимальный выход 3.09 МГц, что противоречит условию. То есть, с её помощью режим LP Run не получить.

Re: Что есть System Clock

Ср ноя 01, 2023 06:27:08

Поглядел по stm32g030 - всё там работает... для всей периферии указано потребление при LP Run

Это да, в даташите потребление есть. А вот если открыть RM, то там в списке периферии часть её в LPRun не работает (а по факту работает).

Re: Что есть System Clock

Ср ноя 01, 2023 07:08:57

Ну, CAN я не знаю, а вот USB.... работает на 2 МГц? Да ещё без внешнего кварца?

Re: Что есть System Clock

Ср ноя 01, 2023 08:10:03

По USB как раз попроще, т.к. частоты по спецификации фиксированы, он вообще по своей схеме тактирования ни в одном из вариантов не тактируется от SYSCLK/HCLK/PCLK (а напрямую от HSI48/PLLQ/HSE). А вот FDCAN работает от PCLK, и там чем ниже частота тактирования, тем просто ниже доступный максимальный битрейт.