stm32f4 usart+DMA

Вс янв 30, 2022 06:47:57

Решил я передать данные с usart при помощиu DMA.А тут вопрос есть у меня функция передачи строки.Она уже не годится.Что мне нужно как преобразовать данную функцию.Что бы передать через DMA. DMA немного изучил.И в серииF1 F4.Там просто каналы .А там стрим и каналы.DMA +ADC там всё понятно.Сколько выводов ADC я использую столько и выставляется бит событий.А тут как?

Re: stm32f4 usart+DMA

Вс янв 30, 2022 09:34:59

Аналогично. Один поток на приём, другой на передачу.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 12:05:27

Это я понял.А вот функция передачи и приёма поменяется?

Re: stm32f4 usart+DMA

Вс янв 30, 2022 14:43:49

Функция передачи:

Настраиваем DMA на отправку, указываем, откуда, куда, сколько. Запускаем передачу.

Функция приёма:

Ловим прерывание UART_IDLE, проверяем значение DMAx_Stream_y->NDTR, обновляем (по желанию, если это не кольцевой буфер у DMA) указатели на память, разрешаем работу канала DMA (если бит разрешения сбросился). Потом обрабатываем полученные данные.

ИМХО, на STM32F407 работает как раз таким образом. Код давать не буду - ещё прошлый вопрос не победили.

Настраиваем DMA на отправку, указываем, откуда, куда, сколько. Запускаем передачу.

Функция приёма:

Ловим прерывание UART_IDLE, проверяем значение DMAx_Stream_y->NDTR, обновляем (по желанию, если это не кольцевой буфер у DMA) указатели на память, разрешаем работу канала DMA (если бит разрешения сбросился). Потом обрабатываем полученные данные.

ИМХО, на STM32F407 работает как раз таким образом. Код давать не буду - ещё прошлый вопрос не победили.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 14:49:55

Кстати, мне всегда было интересно, как быть с приёмом и таймаутами. Передача - это элементарно. А с приёмом, если размер неизвестен, то нужно как-то ловить таймаут после последнего принятого байта. И как узнать размер (кол-во принятый байт) ?

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 18:14:04

Кстати, мне всегда было интересно, как быть с приёмом и таймаутами. Передача - это элементарно. А с приёмом, если размер неизвестен, то нужно как-то ловить таймаут после последнего принятого байта. И как узнать размер (кол-во принятый байт) ?

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

С DMA тоже просто:

1. Запускаем приём некоторого блока символов в FIFO. Разрешив прерывание по завершении приёма этого блока. Получили прерывание: обновляем указатель позиции заполненности FIFO и перезапускаем DMA на приём следующего блока символов.

2. Параллельно имеем некое периодическое прерывание (от таймера). В котором проверяем текущую позицию приёма DMA (или счётчик - смотря что имеется в конкретном МК). Видим изменение позиции - обновляем указатель позиции заполненности FIFO.

Можно при этом работать по DMA в непрерывном режиме (двойной буфер или linked list или тому подобное - смотря что имеется в конкретном МК).

Re: stm32f4 usart+DMA

Вс янв 30, 2022 18:35:33

Кстати, мне всегда было интересно, как быть с приёмом и таймаутами. Передача - это элементарно. А с приёмом, если размер неизвестен, то нужно как-то ловить таймаут после последнего принятого байта. И как узнать размер (кол-во принятый байт) ?

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

У СТМ в МК применяется два разных UART: полноценный и кастрированный. Линейки F0 и F7 оснащаются полноценным, F1 и F4- кастрированным. В F3- нужно смотреь конкретный МК, есть и те, и другие.

Все промышленные протоколы имеют два признака конца посылки: специальный символ конца сообщения или пауза между байтами. Поэтому в полноценном UART есть настройка прерывания по приёму программируемого байта или по программируемой задержке RTO, измеряемой в битах. В кастрированных UART тебе доступно только прерывание по паузе в 20 бит между байтами, которое используется как детектор ошибки в Модбас.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 18:46:33

Кстати, мне всегда было интересно, как быть с приёмом и таймаутами. Передача - это элементарно. А с приёмом, если размер неизвестен, то нужно как-то ловить таймаут после последнего принятого байта. И как узнать размер (кол-во принятый байт) ?

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Без DMA это делает просто. Перезапуск таймера в прерывании по каждому байтику.

Кристалл F407 (с "кастрированным" UART'ом):

Используется прерывание USART:IDLE, соответственно, ожидаем не принятия ОДНОГО байта, а принятие некоторого количества непрерывных байт (без пауз, либо с паузами меньше длины одного фрейма (10 битовых тайм-слотов - START + 8 + STOP)).

- Код:

void USART1_IRQHandler(void) {

if (USART1->SR & USART_SR_IDLE) {

(void)USART1->DR; // Очистка флага IDLE. Мне лично кажется такой подход странным, но так сказано в RM на кристалл. Окей.

// Взводим флаг, что данные были приняты

BOX_CON_RX_DONE = 1;

// Проверяем, что значение счётчика DMA_Stream->NDTR изменилось

if ((sizeof(BoxCon_RX_BUF) - DMA2_Stream5->NDTR) != DMA_BUF_START_LAST) {

// Запоминаем позиции в другие масивы. В итоге получаем ссылки на адреса в кольцевом буфере, без, собственно, ссылок.

DMA_BUF_START[DMA_CURR_WR_BUF] = DMA_BUF_START_LAST;

DMA_BUF_START_LAST = (sizeof(BoxCon_RX_BUF) - DMA2_Stream5->NDTR);

DMA_BUF_END[DMA_CURR_WR_BUF] = DMA_BUF_START_LAST;

// Выбираем следующий указатель (там не указатель, но суть похожа)

DMA_CURR_WR_BUF++;

// Проверяем, и если он последний - возвращаемся в начало.

if (DMA_CURR_WR_BUF >= (MAX_DMA_BUFFERS_COUNT)) { DMA_CURR_WR_BUF = 0; };

};

};

};

В коде выше не объявлены:

1. Кольцевой буфер (у меня в коде он размером 2кБ)

2. Три массива указателей (технически, это индексы), uint16_t, количеством MAX_DMA_BUFFERS_COUNT

3. volatile переменная BOX_CON_RX_DONE, являющаяся флагом наличия данных в буфере для процесса, который занимается их обработкой

Знаю, можно было использовать примитив xQueueSendFromISR(...);, но код работает и так, максимально быстро, минимально используя абстракции RTOS. А раз не использует абстракции - то и не требует работы с контекстом, или внутренних рутин самой RTOS, что позволяет проводить в этом прерывании минимально возможное время.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 19:10:45

Спойлер

- Код:

Используется прерывание USART:IDLE,

Где это написано? Покажите.DMA и прирываниеIDLE USART?

Re: stm32f4 usart+DMA

Вс янв 30, 2022 21:14:55

Все промышленные протоколы имеют два признака конца посылки: специальный символ конца сообщения или пауза между байтами.

Это не так. Разнообразие протоколов гораздо богаче. Например: АТ-командные протоколы обмена. Не поможет там Вам ни то ни другое.Добавлено after 17 minutes 46 seconds:

Используется прерывание USART:IDLE, соответственно, ожидаем не принятия ОДНОГО байта, а принятие некоторого количества непрерывных байт

А как именно работает это прерывание IDLE - знаете? А то в мануале оно очень туманно описано. И не факт, что удастся использовать его совместно с DMA.И причём (насколько знаю): в разных STM32 есть разные средства обнаружения таймаута на UART.RXD. В младших, слыхал, есть RTOF, который похож, но не совсем.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 21:23:51

Ух, сколько всего написали  Спасибо всем, буду переваривать информацию

Спасибо всем, буду переваривать информацию

У меня будет задача проста, никаких Модбасов, никаких строк, ... Приём пакета, размером в n байт, где n - неизвестная. Окончание пакета - таймаут (длина - 5...10 байт). Камушек будет, вероятнее всего, F405RGT.

У меня будет задача проста, никаких Модбасов, никаких строк, ... Приём пакета, размером в n байт, где n - неизвестная. Окончание пакета - таймаут (длина - 5...10 байт). Камушек будет, вероятнее всего, F405RGT.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 23:18:13

в RM Не написано такого.И в нете нет таких примеров я с stm32 недавно 2.5 года.DMA и прерывание по DMA используется с USARTэто так.Но не прерывании по USART IDLE .Почему я так говорю.Все примеры которые я знаю и видел.Когда включают DMA .Обязательно выключают прерывание перфериии(USART.ADC .SPI и тд.).Пускай приведёт пример .Я включал ADC+DMA.Я выключаю прерывание по ADC.Иначе работать не будет.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 23:22:12

Ух, сколько всего написали  Спасибо всем, буду переваривать информацию

Спасибо всем, буду переваривать информацию

У меня будет задача проста, никаких Модбасов, никаких строк, ... Приём пакета, размером в n байт, где n - неизвестная. Окончание пакета - таймаут (длина - 5...10 байт). Камушек будет, вероятнее всего, F405RGT.

Не самая удачная комбинация МК и протокола.

У меня будет задача проста, никаких Модбасов, никаких строк, ... Приём пакета, размером в n байт, где n - неизвестная. Окончание пакета - таймаут (длина - 5...10 байт). Камушек будет, вероятнее всего, F405RGT.

Если делать на DMA + периодическое прерывание, то нужна будет довольно приличная частота периодических прерываний. Такая, чтобы за время паузы гарантированно успевало произойти как минимум 2 периодических прерывания. Т.е. - на интервал 5 байт получается = 2 прерывания. Такая высокая частота ставит под вопрос пользу применения DMA. Польза эта будет весьма мала.

Можно было бы использовать прерывание RX-таймаута от UART. Вроде в UART-ах STM32F4xx есть какое-то прерывание IDLE, но судя по его описанию в мануале - оно происходит если в потоке данных на UART.RX возникла пауза (как минимум определённое число битовых интервалов), после которой получен старт-бит нового байта. Тогда использовать его как маркер конца кадра не получится. Но если всё-таки оно сигнализирует именно об отсутствии активности на RXD - тогда можно. Здесь: https://electronix.ru/forum/index.php?a ... nt=1779579 автор пишет, что IDLE всё-таки сигнализирует об отсутствии активности на RXD. Но я бы лучше проверил это.

PS: Если есть возможность, я бы лучше поменял протокол на другой, не привязанный к времянкам.

Либо поменял бы МК на другой -> имеющий аппаратный FIFO в UART с прерыванием таймаута. Например NXP-ные Cortex-ы имеют такие UART-ы.

А Infineon-овские XMC4xxx, хоть и не имеют прерывания неактивности RXD, но позволяют внутренне пробросить RXD на любой таймер и отслеживать неактивность с его помощью. И очень гибко.

Re: stm32f4 usart+DMA

Вс янв 30, 2022 23:31:12

Вот же, всё есть :ivan dimir писал(а):Но не прерывании по USART IDLE

Спойлер

Вы покажите пример который работает и который не работает. И Вам подскажут, что делаете не так.ivan dimir писал(а):Я включал ADC+DMA.Я выключаю прерывание по ADC.Иначе работать не будет.

Добавлено after 4 minutes 39 seconds:

jcxz, протокол уже существует, его не поменять. А на счёт DMA, если и не получится, то и фиг с ним - сделаю по классической схеме - перезавод таймера в прерывании по RX. Работать будет, никуда не денется

Re: stm32f4 usart+DMA

Пн янв 31, 2022 00:24:33

Спойлер

- Код:

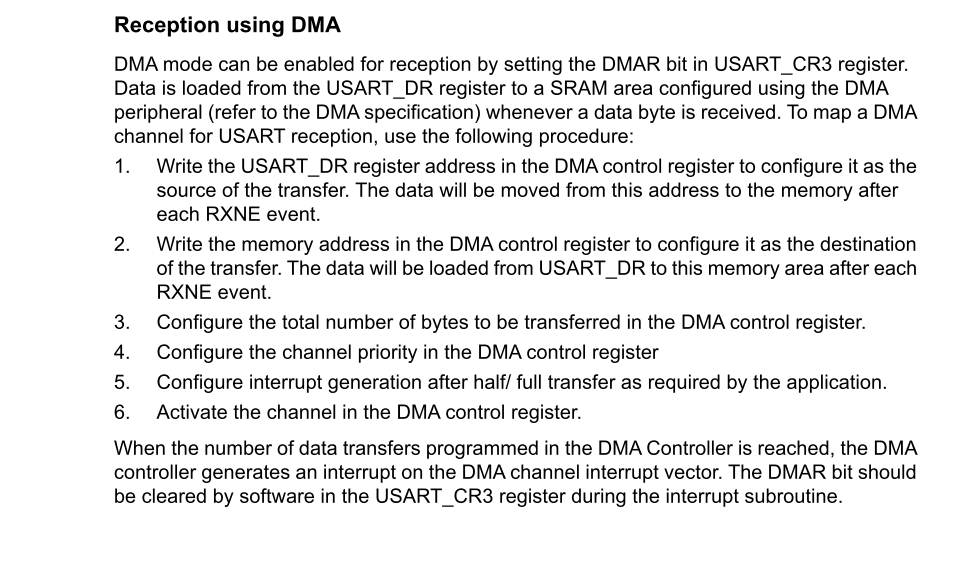

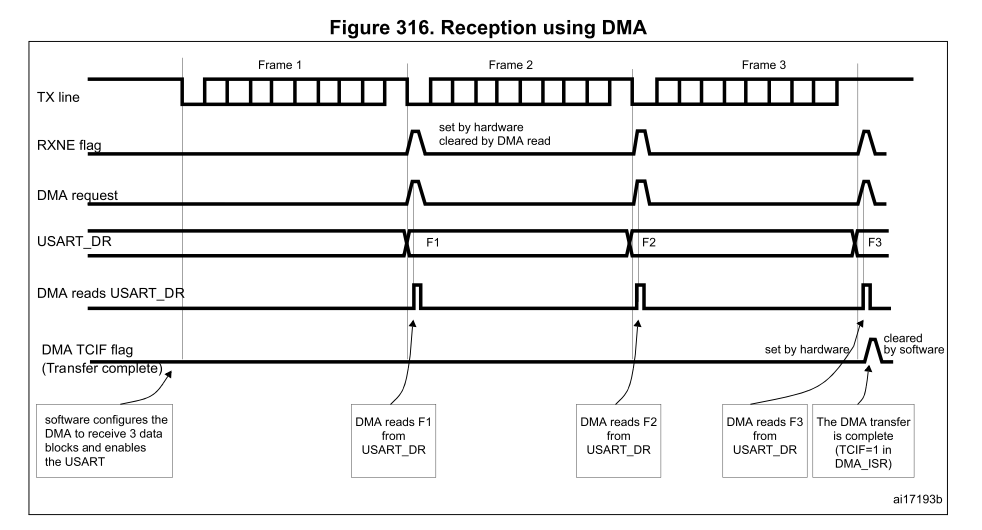

Прием с использованием DMA

Режим DMA можно включить для приема, установив бит DMAR в регистре USART_CR3.

Данные загружаются из регистра USART_DR в область SRAM, сконфигурированную с помощью DMA.

периферийное устройство (см. спецификацию DMA) всякий раз, когда принимается байт данных. Чтобы отобразить прямой доступ к памяти

канала для приема USART используйте следующую процедуру:

1. Запишите адрес регистра USART_DR в регистр управления DMA, чтобы сконфигурировать его как

источник перевода. Данные будут перемещены с этого адреса в память после

каждое событие RXNE.

2. Запишите адрес памяти в управляющий регистр прямого доступа к памяти, чтобы настроить его как место назначения.

передачи. Данные будут загружаться из USART_DR в эту область памяти после каждого

RXNE-событие.

3. Настройте общее количество байтов для передачи в регистре управления DMA.

4. Настройте приоритет канала в регистре управления DMA.

5. Настройте генерацию прерывания после половинной/полной передачи в соответствии с требованиями приложения.

6. Активируйте канал в регистре управления DMA.

Когда количество передач данных, запрограммированное в контроллере DMA, достигнуто, DMA

контроллер генерирует прерывание по вектору прерывания канала DMA. Бит DMAR должен

быть очищенным программным обеспечением в регистре USART_CR3 во время подпрограммы прерывания

Добавлено after 5 minutes 49 seconds:

Спойлер

- Код:

Пометка ошибок и генерация прерываний в многобуферной связи

В случае многобуферной связи, если во время транзакции возникает какая-либо ошибка, флаг ошибки

будет утвержден после текущего байта. Прерывание будет сгенерировано, если разрешение прерывания

установлен флаг. Для ошибки кадрирования, ошибки переполнения и флага шума, которые устанавливаются с помощью RXNE в

В случае приема одного байта будет отдельный бит разрешения прерывания флага ошибки (бит EIE в

регистр USART_CR3), который, если он установлен, вызовет прерывание после текущего байта с

любая из этих ошибок.

Re: stm32f4 usart+DMA

Пн янв 31, 2022 00:32:04

Значит я не понял Вас. Задайте нормально вопрос. Чётко, внятно и развёрнуто. А не в своём стиле - кусками из мыслей.

Добавлено after 2 minutes 41 second:

Вы процитировали описания из RM :

Что Вы этим хотели сказать - не понятно

Добавлено after 2 minutes 41 second:

Вы процитировали описания из RM :

Спойлер

Re: stm32f4 usart+DMA

Пн янв 31, 2022 00:46:53

Я хотел сказать Что сдесь нет IDLE.IDLE-пустой(праздный) -перевод по приёму.

Re: stm32f4 usart+DMA

Пн янв 31, 2022 01:02:37

Вас трудно понять.

IDLE советуют использовать как детект окончания приёма. Он вообще никак с DMA не связан.

IDLE советуют использовать как детект окончания приёма. Он вообще никак с DMA не связан.

Re: stm32f4 usart+DMA

Пн янв 31, 2022 07:40:36

Эту тему перетрясали неоднократно.

Вы не задали вопрос для чего?, а сразу говорите как.

Если для передачи строки длиной 16 символов, больше телодвижений на по подготовку буфера и включение канала.

Если для передачи килобайтных строк, тогда другой разговор.

Если для приема килобайтных строк, тогда да, делайте что хотите, хоть кольцевой хоть прямой буфер размером в 2кило.

А если для приема простых команд с подключенного компутера, длиной 1-2 символ, в этих буферах смысла нет, что так в прерывании будете проверять что эдак, какой выигрыш?

В последнем коде ТС

Вы не задали вопрос для чего?, а сразу говорите как.

Опять тот же вопрос, для чего?Аlex писал(а):Передача - это элементарно.

Если для передачи строки длиной 16 символов, больше телодвижений на по подготовку буфера и включение канала.

Если для передачи килобайтных строк, тогда другой разговор.

И опять тот же самый вопрос, для чего?Аlex писал(а):А с приёмом, если размер неизвестен,

Если для приема килобайтных строк, тогда да, делайте что хотите, хоть кольцевой хоть прямой буфер размером в 2кило.

А если для приема простых команд с подключенного компутера, длиной 1-2 символ, в этих буферах смысла нет, что так в прерывании будете проверять что эдак, какой выигрыш?

В последнем коде ТС

Спойлер

- Код:

void TIM2_IRQHandler(void) {

if (TIM2 - > SR & TIM_SR_UIF) {

TIM2 - > SR &= ~TIM_SR_UIF;

//IWDG->KR = 0xAAAA;

pauza++;

if (pauza > 40) {

//IWDG->KR = 0xAAAA;

GPIOC - > BSRR |= GPIO_BSRR_BS13;

}

if (pauza > 80) {

GPIOC - > BSRR |= GPIO_BSRR_BR13;

pauza = 0;

}

}

}

void TIM3_IRQHandler(void) {

if (TIM3 - > SR & TIM_SR_UIF) {

TIM3 - > SR &= ~TIM_SR_UIF;

pauza1++;

}

}

void timer_2_init(void) {

RCC - > APB1ENR |= RCC_APB1ENR_TIM2EN;

TIM2 - > PSC = 3500 - 1; // ??????????? ???????? ??? ?????? ????? 1000 ??? ? ???????

TIM2 - > ARR = 100 - 1; //65535

TIM2 - > EGR |= TIM_EGR_UG;

TIM2 - > DIER |= TIM_DIER_UIE;

TIM2 - > CR1 |= TIM_CR1_CEN;

NVIC_EnableIRQ(TIM2_IRQn);

}

void timer_3_init(void) {

RCC - > APB1ENR |= RCC_APB1ENR_TIM3EN;

TIM3 - > PSC = 3500 - 1; // ??????????? ???????? ??? ?????? ????? 1000 ??? ? ???????

TIM3 - > ARR = 100 - 1; //65535

TIM3 - > EGR |= TIM_EGR_UG;

TIM3 - > DIER |= TIM_DIER_UIE;

TIM3 - > CR1 |= TIM_CR1_CEN;

NVIC_EnableIRQ(TIM3_IRQn);

}

Re: stm32f4 usart+DMA

Пн янв 31, 2022 09:11:45

Если для передачи строки длиной 16 символов, больше телодвижений на по подготовку буфера и включение канала.

Это не так. Дал команду на передачу и забыл.Спойлер

- Код:

void Send_USART1_DMA(uint8_t *adr, uint32_t cnt)

{

constexpr uint32_t dma_cfg = _VAL2FLD(DMA_CCR_MSIZE,0) | _VAL2FLD(DMA_CCR_PSIZE,0) | DMA_CCR_DIR | DMA_CCR_MINC;

DMA1_Channel1->CCR = dma_cfg;

DMA1_Channel1->CMAR = (uint32_t) adr; // Чаще всего не надо

DMA1_Channel1->CNDTR = cnt;

DMA1_Channel1->CCR = dma_cfg | DMA_CCR_EN;

}

- Код:

//void Send_USART1_DMA(uint8_t *adr, uint32_t cnt)

//{

// constexpr uint32_t dma_cfg = _VAL2FLD(DMA_CCR_MSIZE, 0) | _VAL2FLD(DMA_CCR_PSIZE, 0) | DMA_CCR_DIR | DMA_CCR_MINC;

// DMA1_Channel1->CCR = dma_cfg;

_Z15Send_USART1_DMAPhj:

LDR R2,??DataTable3_6

MOVS R3,#+144

STR R3,[R2, #+0]

// DMA1_Channel1->CMAR = (uint32_t) adr; // Чаще всего не надо

STR R0,[R2, #+12]

// DMA1_Channel1->CNDTR = cnt;

STR R1,[R2, #+4]

// DMA1_Channel1->CCR = dma_cfg | DMA_CCR_EN;

MOVS R0,#+145

STR R0,[R2, #+0]

//}

BX LR

В последнем коде ТС

Кровь из глаз сочится. Где вы этот говнокод берёте и зачем друг у друга копипастите???