# CSKY Architecture USER GUIDE

# Statement:

C-SKY Microsystems Co., Ltd. reserves all rights of this document. Contents of this document can be altered, updated, deleted or changed, and no further notice will be given.

Copyright © 2001-2018 C-SKY Microsystems Co., Ltd.

Company address: 3 XiDoumen Rd,BldgA,15F,Hangzhou,China Post Code: 310012 Tel: 0571-88157059 Fax: 0571-88157059-8888 Homepage: <u>www.c-sky.com</u> E-mail: info@c-sky.com

# **C-Sky Confidential**

# **Revision history:**

| Revision | Date       | Description   | Author                                        |

|----------|------------|---------------|-----------------------------------------------|

| 1.0      | 12/01/2017 | First release | Hangzhou C-Sky<br>Microsystems<br>Corporation |

# **C-Sky Confidential**

# Table of contents:

| 1. INTR | ODUCTION                                        | 7    |

|---------|-------------------------------------------------|------|

| 1.1. I  | NSTRUCTION MIXING MODE                          | 7    |

| 1.2. F  | PROGRAMMING MODEL                               | 8    |

| 1.3. E  | DATA FORMAT                                     | 9    |

| 2. NAM  | ING CONVENTIONS                                 | . 11 |

| 2.1. 5  | YMBOL                                           | 11   |

|         | ERM                                             |      |

|         |                                                 |      |

|         | STER DESCRIPTION                                |      |

|         | JSER MODE PROGRAM MODEL                         |      |

| 3.1.1   | 1 1 5                                           |      |

| 3.1.2   |                                                 |      |

| 3.1.3   |                                                 |      |

|         | SUPERVISOR MODE PROGRAM MODEL                   |      |

| 3.2.1   |                                                 |      |

| 3.2.2   |                                                 |      |

| 3.2.3   | 5 ( ) )                                         |      |

| 3.2.4   |                                                 |      |

| 3.2.5   |                                                 |      |

| 3.2.6   |                                                 |      |

| 3.2.7   |                                                 |      |

| 3.2.8   | 5 5 1 7 7 7                                     |      |

| 3.2.9   | <b>, , , , , , , , , ,</b>                      |      |

| 3.2.1   |                                                 |      |

| 3.2.1   | 5 5 1 7 7                                       |      |

| 3.2.1   |                                                 |      |

| 3.2.1   | 5 ( , , , ,                                     |      |

| 3.2.1   |                                                 |      |

| 4. 32-B | T INSTRUCTIONS                                  | . 26 |

| 4.1. F  | UNCTIONAL CLASSIFICATION OF 32-BIT INSTRUCTIONS | . 26 |

| 4.1.1   | Data Operation Instructions                     | . 26 |

| 4.1.2   |                                                 | . 28 |

| 4.1.3   |                                                 |      |

| 4.1.4   |                                                 |      |

| 4.1.5   |                                                 |      |

|         | INCODING OF 32-BIT INSTRUCTIONS                 |      |

| 4.2.1   |                                                 |      |

| 4.2.2   |                                                 |      |

| 4.2.3   | -5                                              |      |

|         | PERAND ADDRESSING MODE OF 32-BIT INSTRUCTIONS   |      |

| 4.3.1   | 5 1 11                                          |      |

| 4.3.2   | 5 1 11                                          |      |

| 4.3.3   | Addressing Mode of Register-type Instructions   | 33   |

# **C-Sky Confidential**

| 5. 16-BIT I | NSTRUCTION SET                                          | . 36 |

|-------------|---------------------------------------------------------|------|

| 5.1. FUN    | ICTIONAL CLASSIFICATION OF 16-BIT INSTRUCTIONS          | . 36 |

| 5.1.1.      | Data Operation Instruction                              | . 36 |

| 5.1.2.      | Branch Jump Instruction                                 |      |

| 5.1.3.      | Memory Access Instruction                               | . 38 |

| 5.1.4.      | Privilege Instructions                                  | . 39 |

| 5.2. Cot    | DING MODE OF 16-BIT INSTRUCTIONS                        | . 39 |

| 5.2.1.      | Јитр Туре                                               | . 39 |

| 5.2.2.      | Immediate Operand Type                                  | . 39 |

| 5.2.3.      | Register Type                                           | . 41 |

| 5.3. Ope    | ERAND ADDRESSING MODE OF 16-BIT INSTRUCTIONS            | . 42 |

| 5.3.1.      | Addressing Mode of Jump-type Instructions               | . 42 |

| 5.3.2.      | Addressing Mode of Immediate-type Instructions          | . 42 |

| 5.3.3.      | Addressing Mode of Register-type Instructions           | . 45 |

| 6. EXCEP    |                                                         | 47   |

|             |                                                         |      |

| 6.1. Ove    | ERVIEW OF EXCEPTION HANDLING                            | . 47 |

| 6.2. Exc    | EPTION TYPES                                            | . 49 |

| 6.2.1.      | Reset Exception(offset 0x0)                             |      |

| 6.2.2.      | Misaligned Memory Access Exception (offset 0x4)         | . 50 |

| 6.2.3.      | Access Error Exception (offset 0x8)                     |      |

| 6.2.4.      | Illegal Instruction Exception (offset 0x10)             | . 50 |

| 6.2.5.      | Instruction Privilege Violation Exception (offset 0x14) | . 50 |

| 6.2.6.      | Break-point Exception (offset 0x1C)                     | . 50 |

| 6.2.7.      | Unrecoverable Exception (offset 0x20)                   | . 51 |

| 6.2.8.      | Interrupt Exception                                     |      |

| 6.2.9.      | Trap Exception (offset 0x40-0x4C)                       |      |

| 6.3. Exc    | EPTION PRIORITY                                         | . 52 |

| 6.3.1.      | Debug Request while Handling Exceptions                 | . 53 |

| 6.4. Ret    | URN FROM EXCEPTION                                      | . 53 |

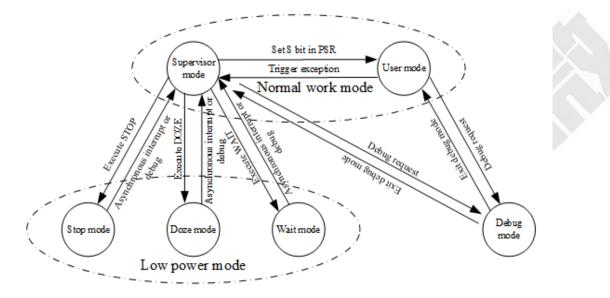

| 7. WORK     | MODE SWITCHING                                          | . 54 |

| 7.1. CSI    | YCPU Work Mode and Switching                            | 54   |

| 7.1.1.      | Normal Mode                                             |      |

| 7.1.2.      | Low Power Mode                                          |      |

| 7.1.3.      | Debug Mode                                              |      |

|             | -                                                       |      |

| APPENDIX    | A: EXAMPLE OF SETTING MPU                               | . 56 |

| APPENDIX    | B: TERM LIST OF BASIC INSTRUCTIONS                      | . 58 |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

|             |                                                         |      |

# **C-Sky Confidential**

# LIST OF CHARTS:

| CHART 1-1 MIXING PRINCIPLE OF 32-BIT/16-BIT INSTRUCTIONS               | 8    |

|------------------------------------------------------------------------|------|

| CHART 1-2 PROGRAM MODEL                                                | 8    |

| CHART 1-3 DATA STRUCTURE IN MEMORY                                     | 9    |

| CHART 1-4 DATA STRUCTURE IN REGISTER                                   | . 10 |

| CHART 3-1 USER MODEL REGISTER                                          | . 14 |

| CHART 3-2 ADDITIONAL RESOURCES IN SUPERVISOR MODEL                     | . 16 |

| CHART 3-3 PROCESSOR STATUS REGISTER                                    | . 17 |

| CHART 3-4 VECTOR BASE REGISTER                                         | . 19 |

| CHART 3-5 CACHE CONFIGURE REGISTER                                     | . 20 |

| CHART 3-6 MEMORY PROTECTION SETTING                                    | . 20 |

| CHART 3-7 CACHEABILITY AND ACCESS PERMISSION REGISTER                  | . 21 |

| CHART 3-8 ACCESS PERMISSION SETTING                                    | . 21 |

| CHART 3-9 PROTECTION REGION CONTROL REGISTER                           | . 21 |

| CHART 3-10 PROTECTION REGION SIZE SETTING AND BASE ADDRESS REQUIREMENT | . 22 |

| CHART 3-11 PROTECTION REGION SELECT REGISTER                           |      |

| CHART 3-12 CPU HINT REGISTER                                           |      |

| CHART 4-1 LIST OF 32-BIT ADD/SUB INSTRUCTIONS                          | . 26 |

| CHART 4-2 LIST OF 32-BIT COMPARISON INSTRUCTIONS                       |      |

| CHART 4-3 LIST OF 32-BIT DATA TRANSFER INSTRUCTIONS                    |      |

| CHART 4-4 LIST OF 32-BIT BIT INSTRUCTIONS                              | . 28 |

| CHART 4-5 LIST OF 32-BIT EXTRACT AND INSERT INSTRUCTIONS               | . 28 |

| CHART 4-6 LIST OF 32-BIT MUL AND DIV INSTRUCTION                       | . 28 |

| CHART 4-7 LIST OF OTHER 32-BIT ARITHMETIC INSTRUCTIONS                 | . 28 |

| CHART 4-8 LIST OF 32-BIT BRANCH INSTRUCTIONS                           | . 28 |

| CHART 4-9 LIST OF 32-BIT JUMP INSTRUCTION                              | . 28 |

| CHART 4-10 LIST OF 32-BIT IMMEDIATE OPERAND OFFSET ACCESS INSTRUCTION  | . 29 |

| CHART 4-11 LIST OF 32-BIT LOW POWER CONSUMPTION INSTRUCTIONS           | . 29 |

| CHART 4-12 LIST OF 32-BIT ABNORMAL RETURN INSTRUCTIONS                 | . 29 |

| CHART 4-13 LIST OF 32-BIT SPECIAL FUNCTION                             | . 30 |

| CHART 5-1 LIST OF 16-BIT ADD/SUB INSTRUCTIONS                          | . 36 |

| CHART 5-2 LIST OF 16-BIT LOGICAL OPERATION INSTRUCTIONS                | . 36 |

| CHART 5-3 LIST OF 16-BIT SHIFT INSTRUCTIONS                            | . 37 |

| CHART 5-4 LIST OF 16-BIT COMPARE INSTRUCTIONS                          | . 37 |

| CHART 5-5 LIST OF 16-BIT DATA TRANSFER INSTRUCTIONS                    | . 37 |

| CHART 5-6 LIST OF 16-BIT BIT OPERATION INSTRUCTIONS                    | . 37 |

# **C-Sky Confidential**

| CHART 5-7 LIST OF 16-BIT EXTRACT AND INSERT INSTRUCTIONS               | 37 |

|------------------------------------------------------------------------|----|

| CHART 5-8 LIST OF 16-BIT MULTIPLY-DIVIDE INSTRUCTIONS                  | 38 |

| CHART 5-9 LIST OF 16-BIT JUMP INSTRUCTIONS                             | 38 |

| CHART 5-10 LIST OF 16-BIT IMMEDIATE OPERAND OFFSET ACCESS INSTRUCTIONS | 38 |

| CHART 5-11 LIST OF 16-BIT MULTI-REGISTER ACCESS INSTRUCTION            | 38 |

| CHART 5-12 LIST OF 16-BIT BINARY TRANSLATED STACK INSTRUCTIONS 错误!未定义书 | 签。 |

| CHART 5-13 LIST OF 16-BIT PRIVILEGE INSTRUCTIONS                       | 39 |

| CHART 7-1 EXCEPTION VECTOR TABLE                                       | 48 |

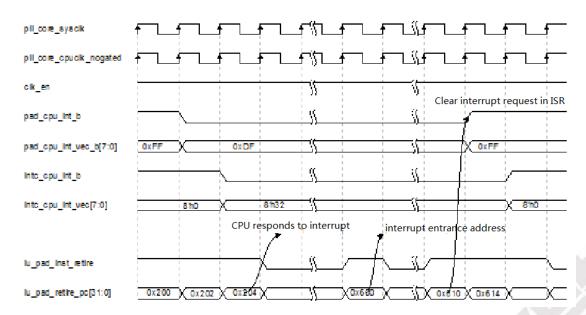

| CHART 7-2 PROCESS OF HANDLING INTERRUPT                                | 52 |

| CHART 7-3 EXCEPTION PRIORITY                                           | 53 |

| CHART 8-1 CPU WORK MODES                                               | 54 |

# **C-Sky Confidential**

# 1. Introduction

CSKY instruction set architecture(ISA) refers to the second-generation independent intellectual property instruction set architecture of CK-Core family. CSKY ISA has characteristics like high performance, high code density, low power consumption and extensibility. CSKY ISA is designed by directing at different demands for embedded applications of high performance and low power consumption in the future. 32-bit/16-bit mixed length encoding is adopted. Among them, with perfect functions, 32-bit instruction is used to improve the comprehensive performance of instruction set; as the subset of 32-bit instruction, 16-bit instruction possesses relatively simple functions, and it is applied to improve instruction code density and to reduce power consumption.

Main characteristics of CSKY instruction set architecture are as follows:

- 32/16-bit instructions are realized by way of hybrid coding, and no performance loss will be caused in the process of instruction switch;

- As a complete set of instruction set architecture, 32-bit instructions have perfect functions and excellent performance;

- Most 16-bit instructions are subsets of 32-bit instructions and they can realize instructions with the highest frequency in 32-bit instructions;

- 32-bit instructions adopt 32 general-purpose registers and 3-operand addressing mode;

16-bit instructions adopt 16 general-purpose registers and 2-operand addressing mode.

# 1.1. Instruction mixing mode

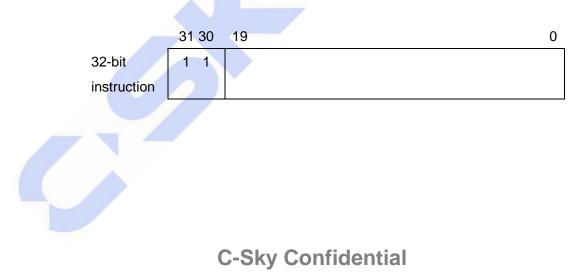

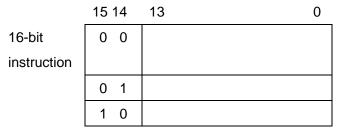

CSKY distinguishes 32-bit instructions from 16-bit instructions through two highest bits in instruction codes. As for the two highest bits, 11 represents 32-bit instruction and the other one means 16-bit instruction. The specific instruction mixing mode is presented in Chart 1.1.

# 1.2. Programming model

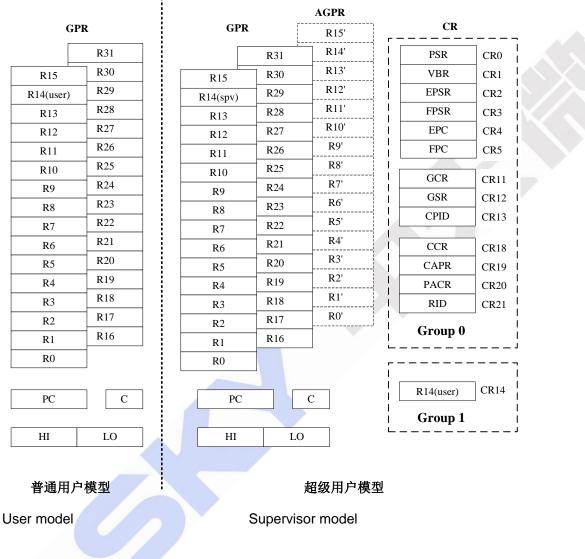

Chart 1-2 program model

CSKY defines two operation modes: user mode and supervisor mode. When the S bit in PSR is set, processor operates under supervisor mode. Also, it changes to supervisor mode after reset.

The above two operation modes are corresponding to different operation rights, and C-Sky Confidential

their differences are mainly reflected in two aspects: 1) access to the register; 2) use of privileged instructions; 3) access to the control register of tightly coupled IP. User mode is only allowed to access general purpose register while supervisor mode is allowed to access all general purpose register and control register. In this way, user mode program can be prevented from privilege information, and operating system provides management and service for user mode program by coordinating with the user mode program. While in supervisor mode, the program can access all control register of tightly coupled IP to schedule CPU resources.

In the user mode, the program is permitted to access user stack pointer (user SP), but not supervisor stack pointer (spv SP).

In the user mode, the program is permitted to access link register (LR) shared with supervisor mode.

Under user mode, condition/carry bit (C) is located in the lowest bit of PSR, and it can be accessed and changed by common user instructions. It is the only data bit that can be visited under user mode in PSR.

Most instructions can be used under user mode, except for some privilege ones such as stop, doze, wait, mfcr, mtcr, rte which may greatly influence the system. Besides, trap #n instruction can be used to change from user mode to supervisor mode.

In the supervisor mode, all general purpose registers and control registers can be accessed. In addition, both user SP and spv SP are accessible. To access user SP under supervisor mode, mtcr rx cr<14, 1> and mfcr rz cr<14, 1> instructions should be used.

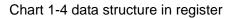

# 1.3. Data format

# **C-Sky Confidential**

| 2          | 4bit signed S e | S Byte  | Signed |                                       |

|------------|-----------------|---------|--------|---------------------------------------|

|            | 24bit 0 exter   | nsion   | Byte   | single byte<br>Unsigned<br>single byt |

| 16bit sign | ed S extension  | S Byte1 | Byte0  | signed<br>double byt                  |

| 16bit C    | extension       | Byte1   | Byte0  | Unsigned<br>double byt                |

| Byte3      | Byte2           | Byte1   | Byte0  | word                                  |

CSKY supports two's complement integer. The length of operand in every instruction can be explicitly encoded in the program (load/store instruction), or implicitly indicated in instruction operation (index operation, byte extraction). Usually, instructions generate 32-bit results with 32-bit operands.

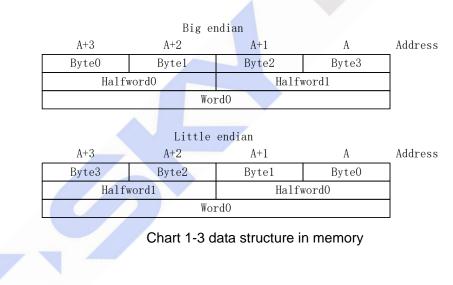

The memory of CSKY can be configured to big endian or little endian. The highest byte of word 0 is located in the address 0 under big endian mode while it is located in the address 3 under little endian mode (default mode). The 31<sup>st</sup> bit is the MSB in the register.

# **C-Sky Confidential**

# 2. Naming conventions

# 2.1. Symbol

The standard symbols and operators used in this document list below:

| symbol            | function              |  |

|-------------------|-----------------------|--|

| +                 | Add                   |  |

| -                 | Subtract              |  |

| *                 | Multiply              |  |

| /                 | Divide                |  |

| >                 | Greater than          |  |

| <                 | Less than             |  |

| =                 | Equal                 |  |

| ≥                 | Greater or equal than |  |

| ≤                 | Less or equal than    |  |

| 1/4               | Not equal             |  |

|                   | AND                   |  |

| +                 | OR                    |  |

| $\oplus$          | XOR                   |  |

| NOT               | NOT                   |  |

| :                 | concatenate           |  |

| $\Rightarrow$     | Transfer              |  |

| $\Leftrightarrow$ | Exchange              |  |

| ±                 | deviation             |  |

| 0b0011            | Binary number         |  |

| 0x0F              | Hexadecimal number    |  |

# 2.2. Term

- Logic 1 represents the true value of Boolean logic.

- Logic 0 represents the false value of Boolean logic.

- Set means change one or more bits to logic 1 value.

# **C-Sky Confidential**

- Clear means change one or more bits to logic 0 value.

- Reserved bit is reserved for function extension, and its value should be 0 without further explanation.

- Signal is an electric current or electromagnetic field used to convey data by transforming states.

- Pin is an external electric physical connection, and a single pin can be connected with multiple signals.

- Enable means make some discrete signal in an effective state:

- Active-low signal changes from high to low;

- Active-high signal changes from low to high.

- Disable means make some enabled signal change state:

- Active-low signal changes from low to high;

- Active-high signal changes from high to low.

- LSB represents the lowest significant bit, and MSB represents the highest significant bit.

- The memory and register apply big endian mode when "pad\_sysio\_bigend\_b=0", which means the highest byte locates at the lowest address. Namely, a word start with the highest byte (bit 31-24).

- Little endian is adopted when "pad\_sysio\_bigend\_b=1".

- Signal, bit field, control bit use a common rule.

- Identifier followed by the numbers from high to low which indicating range, represents a set of signal. For example, addr[4:0] represents a set of address bus, and addr[4] is the MSB while addr[0] is the LSB.

- Single identifier represents single signal. For example, pad\_cpu\_rst\_b means a single signal. Sometimes it is meaningful to add number after identifier. For instance, addr15 means the 16<sup>th</sup> bit of a set of bus.

# **C-Sky Confidential**

# 3. Register description

This chapter mainly introduces the architecture of general purpose registers and control registers in CSKY under user mode or supervisor mode.

# 3.1. User mode program model

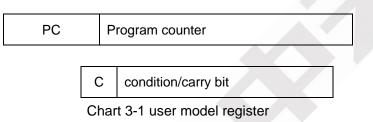

Chart 3-1 lists some registers under user model:

- 32 32-bit general purpose registers(R31~R0)

- 32-bit program counter(PC)

- Condition / carry bit(C bit)

| Name      | Function                                 |  |  |  |  |  |

|-----------|------------------------------------------|--|--|--|--|--|

|           | Undetermined, the first parameter called |  |  |  |  |  |

| R0        | by function                              |  |  |  |  |  |

|           | Undetermined, the second parameter       |  |  |  |  |  |

| R1        | called by function                       |  |  |  |  |  |

| R2        | Undetermined, the third parameter        |  |  |  |  |  |

|           | called by function                       |  |  |  |  |  |

| R3        | Undetermined, the fourth parameter       |  |  |  |  |  |

|           | called by function                       |  |  |  |  |  |

| R4        | Undetermined                             |  |  |  |  |  |

| R5        | Undetermined                             |  |  |  |  |  |

| R6        | Undetermined                             |  |  |  |  |  |

| R7        | Undetermined                             |  |  |  |  |  |

| R8        | Undetermined                             |  |  |  |  |  |

| R9        | Undetermined                             |  |  |  |  |  |

| R10       | Undetermined                             |  |  |  |  |  |

| R11       | Undetermined                             |  |  |  |  |  |

| R12       | Undetermined                             |  |  |  |  |  |

| R13       | Undetermined                             |  |  |  |  |  |

| R14(user) | Stack pointer(user model)                |  |  |  |  |  |

| R15       | Link register                            |  |  |  |  |  |

| R16       | Undetermined                             |  |  |  |  |  |

| R17       | Undetermined                             |  |  |  |  |  |

# **C-Sky Confidential**

| R18 | Undetermined |

|-----|--------------|

| R19 | Undetermined |

| R20 | Undetermined |

| R21 | Undetermined |

| R22 | Undetermined |

| R23 | Undetermined |

| R24 | Undetermined |

| R25 | Undetermined |

| R26 | Undetermined |

| R27 | Undetermined |

| R28 | Undetermined |

| R29 | Undetermined |

| R30 | Undetermined |

| R31 | Undetermined |

|     |              |

# 3.1.1.General purpose register

General purpose registers contains operands, results and address information of the instruction. For both hardware and software, these registers are conventionally used for link call of subprogram, parameter pass and stack pointer, etc.

Among those registers, R14 is the user stack pointer under user mode, and its index is same as other general purpose registers.

# 3.1.2. Program counter

Program counter contains the current address of executing instructions. The value of program counter cannot be modified by instruction directly, instead the processor will automatically accumulate program counters or place a new value into the program counter according to the program operation situations during normal operation or exception handling of program. For some special instructions, program counter can also **C-Sky Confidential**

participate in calculation as relative address. In addition, the low bit in program counter is 0 all the time.

# 3.1.3.Condition / carry bit

Condition or carry bit represents the result after one operation. Condition/carry bit can be clearly set according to the results of compare instructions or unclearly set as some high-precision arithmetic or logical instructions. In addition, special instructions such as XTRB[0-3] will influence the value of condition/carry bit.

# 3.2. Supervisor mode program model

System programmer utilizes supervisor mode to set system operation function, I/O control and other restricted operation.

Supervisor model consists of general purpose registers and other registers below, listed as Chart 3-2:

- 1 supervisor mode stack pointer register(R14)

- Processor Status Register(PSR);

- Vector Base Register(VBR);

- Exception Program Counter (EPC);

- Exception Processor Status Register (EPSR);

- 32-bit Global Control Register (GCR)(configurable width)\*;

- 32-bit Global Status Register (GSR)(configurable width)\*;

- CPU Identification Register (CPUIDR);

- Cache Configure register (CCR);

- Cacheability and Access Permission Register (CAPR) \*;

- Protection region Control Register (PACR) \*;

- Protection Region Select Register (PRSR) \*;

- CPU Hint Register (CHR).

\*note: The selectable register is valid only for specific configurations.

# **C-Sky Confidential**

| PSR   | <cr0,0></cr0,0>   |

|-------|-------------------|

| VBR   | <cr1,0></cr1,0>   |

| EPSR  | <cr2,0></cr2,0>   |

| EPC   | <cr4,0></cr4,0>   |

| GCR   | <cr11,0></cr11,0> |

| GSR   | <cr12,0></cr12,0> |

| CPUID | <cr13,0></cr13,0> |

| CCR   | <cr18,0></cr18,0> |

| CAPR  | <cr19,0></cr19,0> |

| PACR  | <cr20,0></cr20,0> |

| PRSR  | <cr21,0></cr21,0> |

| CHR   | <cr31,0></cr31,0> |

|       |                   |

General Purpose Register

R14(SP,spv)

**Control Register**

Chart 3-2 additional resources in supervisor model

### 3.2.1. Supervisor mode stack pointer R14(spv SP)

In supervisor mode, indexing R14 will automatically select R14(spv SP), which is used as the stack pointer for supervisor mode.

In the meantime, R14(user sp) is not accessible directly. To access user SP under supervisor mode, mfcr/mtcr cr<14, 1> instructions should be used.

# 3.2.2.Processor status register(PSR,CR<0,0>)

Processor status register (PSR) stores the current status and control information of processor, including C bit, interrupt enable bit and other control bits. In the supervisor mode, software is able to access processor status register (PSR). And the S bit in the PSR indicates whether the processor stays at supervisor mode or user mode. In addition, other control bits in PSR indicate whether the EPSR and EPC can store the current content or whether the interrupt is effective.

# **C-Sky Confidential**

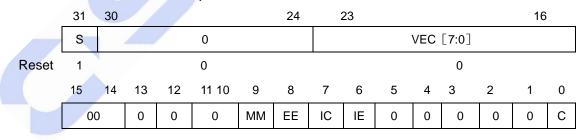

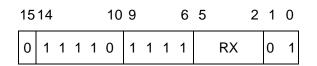

Chart 3-3 processor status register

### S-Supervisor mode set bit:

When S equals 0, the processor works under user mode;

When S equals 1, the processor works under supervisor mode;

This bit is set by hardware during reset or entering exception handler.

### VEC[7:0]-exception VECtor:

When exception happens, these bits can be used to calculate the entrance address of exception handler, and it will be cleared to zero during reset.

### MM-Misalign exception Mask bit:

When MM equals 0, misalign exception will happen if the address of load/store instruction is misaligned.

When MM equals 1, misalign exception will not happen even if the address of load/store instruction is misaligned. If the processor support misalign access, this misalign address will be used to access memory. If the processor doesn't support misalign access, the misaligned address will be transformed to the aligned address (set lower bits to 0) in order to access the memory. However, in any situation, if the address of multi-cycle memory access instructions (such as STM, LDM, PUSH, POP, NIE, NIR, IPUSH, IPOP, etc.) is misaligned, the misalign exception will happen.

Misalign access operations list below:

- The address 1, 2, 3 of word read access will behave as two word-read accesses on the bus, and the address is 0 and 4 respectively.

- The address 1 of half-word read access will behave as one word-read accesses on the bus, and the address is 0.

- The address 3 of half-word read access will behave as two word-read accesses on the bus, and the address is 0 and 4 respectively.

- The address 1 of word write access will behave as an address 1 byte write, an address 2 half-word write and an address 4 byte write one the bus.

- The address 2 of word write access will behave as an address 2 half-word write and an address 4 half-word write on the bus.

- The address 3 of word write access will behave as an address 3 byte write, an address 4 half-word write and an address 6 byte write on the bus.

- The address 1 of half-word write access will behave as two byte-write accesses on the bus, and the address is 1 and 2 respectively.

- The address 3 of half-word write access will behave as two byte-write accesses on the bus, and the address is 3 and 4 respectively.

This bit will be cleared to zero during reset.

# **C-Sky Confidential**

### **EE-Exception Enable bit:**

When EE equals 0, exception is not effective, and any exception except interrupt will be recognized as unrecoverable exception.

When EE equals 1, exception is effective, all exceptions will be normally responded by using EPSR and EPC.

This bit will be cleared to zero during reset or when the exception is responded by processor.

### **IC-Interrupt Control bit:**

When IC equals 0, interrupt can only be responded between instructions;

When IC equals 1, interrupt can be responded before completion of multi-cycle instructions.

This bit will be cleared to zero during reset, not affected by other exceptions.

### **IE-Interrupt Enable bit:**

When IE equals 0, interrupt is not valid, neither are EPC and EPSR;

When IE equals 1, interrupt is valid (EE bit should be 1, otherwise the interrupt is still invalid):

This bit will be cleared to zero during reset or when the exception is responded by processor.

### **C-Condition / Carry bit**

This bit is used for the condition judgment bit of some instructions.

This bit will be cleared to zero during reset.

### 3.2.2.1. Update PSR

PSR can be updated in several different ways, which will result in different influence.it can be modified by exception response, exception handling and execution of instructions like,rte,mtcr. The modification can be implemented in four ways.

• Exception response and exception handling updating PSR:

Updating PSR is part of calculating the entrance address of exception handler, and it includes S, VEC, IE, EE bits in PSR. The priority of modifying S, VEC, IE, EE bits is higher than calculating the entrance address of exception handler. And changing VEC bit has higher priority than the execution of first instruction in exception handler.

• RTE instruction updating PSR:

Updating PSR is part of the execution of rte instruction, and it may include all bits in PSR. The priority of modifying S, IE, EE bits is higher than fetching the return PC. And changing VEC, MM, IC and C bits has higher priority than the execution of first instruction after return.

• MTCR instruction updating PSR:

# **C-Sky Confidential**

If the target register is CR<0, 0>, updating PSR will be part of the execution of mtcr instruction, and it may changes all bits in PSR. The new PSR value will be used by the following instructions, exceptions and interrupt response.

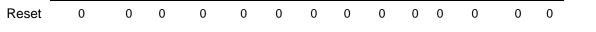

# 3.2.3. Vector Base Register (VBR, CR<1, 0>)

VBR is used for storing the base address of exception vector. It contains 22 high valid bits and 10 reserved bits (the value is 0). The value of VBR is 0X0000000 after reset.

|       | 31 10       | 9        | 0 |

|-------|-------------|----------|---|

|       | VECTOR BASE | RESERVED |   |

| Reset | 0           | 0        |   |

# 3.2.4.Exception Register(CR<2,0>~CR<5,0>)

EPSR and EPC is used for storing current contents when exception occurs. Please refer to chapter 6 for detailed information.

# 3.2.5.Global Control Register (GCR, CR<11, 0>)

Global control register is used to control external devices and events, and it can control specific ones by parallel output interface on the chip. Generally speaking, GCR can be used to manager power, control device, handle events and perform other basic functions by simple setting. User may define which bit in GCR corresponding to which function, and all bits in GCR is readable and writable. Also, the width of GCR is hardware configurable.

# 3.2.6.Global Status Register (GSR, CR<12, 0>)

Global status register is used to mark external devices and events, and it can convey external status to the inside of CPU by the input interface on the chip in order to achieve monitoring. Generally speaking, GSR can be used to monitor the status of external devices and events, and GSR is readable. Also, the width of GSR is hardware configurable.

# 3.2.7. CPU Identification Register (CPUIDRR, CR<13, 0>)

This register is used for storing the internal number of the product developed by C-Sky Microsystems Corporation, and it is read-only register. The value after reset is determined by product itself.

# **C-Sky Confidential**

# 3.2.8. Cache Configure Register (CCR, CR<18, 0>)

Cache configure register is used to configure memory protection region, Endian mode and core-to-bus clock ratio.

|       | 31 | 14 | 13    | 12 11 | 10 8 | 7  | 6 |   | 2 | 1 0 |

|-------|----|----|-------|-------|------|----|---|---|---|-----|

|       | 0  |    | BE_V2 | 0     | SCK  | BE |   | 0 |   | MP  |

| Reset |    |    | 0     |       | -    | -  |   | 0 |   | 0   |

Chart 3-5 Cache Configure register

### **BE\_V2-V2** endian mode:

When BE\_V2 equals 0, not V2 endian mode;

When BE\_V2 equals 1, V2 endian mode;

This bit along with BE decides under which endian mode the processor works. This bit is valid only when BE equals 1.

BE\_V2 should not be changed after being configured during power on reset, and it has corresponding pin on the CPU.

### SCK-core-to-bus clock ratio:

This bit is used to indicate the clock ratio between system bus and CPU core. Its calculation formula is RATIO = SCK + 1, and CPU has corresponding pin. SCK should

not be changed after being configured during power on reset

It has no specific function now, except for software searching.

### **BE-Endian mode:**

When BE equals 0, little endian;

When BE equals 1, big endian;

BE should not be changed after being configured during power on reset, and it has corresponding pin on the CPU.

### MP-Memory protection setting bit:

MP is used to set whether MPU is valid, which lists below:

| MP | Function    |

|----|-------------|

| 00 | MPU invalid |

| 01 | MPU valid   |

Chart 3-6 Memory protection setting

# 3.2.9. Cacheability and Access Permission Register (CAPR,

# CR<19, 0>)

### Each bit of CAPR lists below:

| 31 | 30 | 29         | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| S7 | S6 | <b>S</b> 5 | S4 | S3 | S2 | S1 | S0 | A  | P7 | А  | P6 | A  | P5 | A  | P4 |

# **C-Sky Confidential**

| Reset | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (  | C  | (  | )  | (  | )  | (  | )  |

|-------|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|       | 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|       | A [ | 20 |    | 2  | •  |    |    | 20 | NX |

|       | AF  | -3 | A  | 2  | A  | P1 | AI | >0 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Reset | (   | )  | (  | )  | (  | 0  | (  | )  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Chart 3-7 Cacheability and Access Permission Register

### NX0~NX7-inexecutable attribute setting bit:

When X equals 0, the area is executable;

When X equals 1, the area is inexecutable.

Note: when processor fetches instruction from inexecutable area, access error exception will occur.

### S0~S7-secure attribute setting bit:

When S equals 0, the area is not secure;

When S equals 1, the area is secure.

**Note:** This bit determines the secure attribute of memory access, and this attribute will be conveyed to bus.

### AP0~AP7-access permission setting bit:

| АР | Supervisor permission    | User permission       |

|----|--------------------------|-----------------------|

| 00 | Not accessible           | Not accessible        |

| 01 | Readable and writable    | Not accessible        |

| 10 | Readable and writable    | Read-only             |

| 11 | Readable and<br>writable | Readable and writable |

Chart 3-8 access permission setting

### 3.2.10. Protection region Control Register (PACR,CR<20,0>)

Each bit of PACR lists below:

|       | 31 |              | 10 | 9 | 6 | 5    | 1 | 0 |

|-------|----|--------------|----|---|---|------|---|---|

|       |    | Base Address |    | 0 |   | Size |   | Е |

| Reset |    | <u> </u>     |    | 0 |   | -    |   | 0 |

Chart 3-9 Protection region Control Register

### Base Address-The higher address bits of protection region:

The register indicates the higher address bits of protection region, and the written base address should be aligned with the size of page. For example, if the page size is 8M, CR<20, 0>[22:10] should be 0. The specific requirement of each page lists below: Chart

# **C-Sky Confidential**

3-10 Protection region size setting and base address requirement .

### Size-Protection region size:

The size of protection region ranges from 1KB to 4GB, and it can be calculated through formula: protection region  $=2^{(Size+1)}$ . Hence, the value of size should range from 01001 to 11111, otherwise some unpredictable result may occur.

| Size        | Protection region size | Base address requirement |  |  |  |

|-------------|------------------------|--------------------------|--|--|--|

| 00000—01000 | Reserved               | _                        |  |  |  |

| 01001       | 1KB                    | No requirement           |  |  |  |

| 01010       | 2KB                    | CR<20,0>.bit[10]=0       |  |  |  |

| 01011       | 4KB                    | CR<20,0>.bit[11:10]=0    |  |  |  |

| 01100       | 8KB                    | CR<20,0>.bit[12:10]=0    |  |  |  |

| 01101       | 16KB                   | CR<20,0>.bit[13:10] =0   |  |  |  |

| 01110       | 32KB                   | CR<20,0>.bit[14:10] =0   |  |  |  |

| 01111       | 64KB                   | CR<20,0>.bit[15:10] =0   |  |  |  |

| 10000       | 128KB                  | CR<20,0>.bit[16:10] =0   |  |  |  |

| 10001       | 256KB                  | CR<20,0>.bit[17:10] =0   |  |  |  |

| 10010       | 512KB                  | CR<20,0>.bit[18:10] =0   |  |  |  |

| 10011       | 1MB                    | CR<20,0>.bit[19:10] =0   |  |  |  |

| 10100       | 2MB                    | CR<20,0>.bit[20:10] =0   |  |  |  |

| 10101       | 4MB                    | CR<20,0>.bit[21:10] =0   |  |  |  |

| 10110       | 8MB                    | CR<20,0>.bit[22:10] =0   |  |  |  |

| 10111       | 16MB                   | CR<20,0>.bit[23:10] =0   |  |  |  |

| 11000       | 32MB                   | CR<20,0>.bit[24:10] =0   |  |  |  |

| 11001       | 64MB                   | CR<20,0>.bit[25:10] =0   |  |  |  |

| 11010       | 128MB                  | CR<20,0>.bit[26:10] =0   |  |  |  |

| 11011       | 256MB                  | CR<20,0>.bit[27:10] =0   |  |  |  |

| 11100       | 512MB                  | CR<20,0>.bit[28:10] =0   |  |  |  |

| 11101       | 1GB                    | CR<20,0>.bit[29:10] =0   |  |  |  |

| 11110       | 2GB                    | CR<20,0>.bit[30:10] =0   |  |  |  |

| 11111       | 4GB                    | CR<20,0>.bit[31:10] =0   |  |  |  |

Chart 3-10 Protection region size setting and base address requirement

# **C-Sky Confidential**

### E-Protection region enable setting:

When E equals 0, protection region is disabled;

When E equals 1, protection region is enabled.

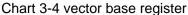

# 3.2.11. Protection Region Select Register(PRSR,CR<21,0>)

PRSR is used to select the current protection region, and each bit lists below:

Chart 3-11 protection region select register

### **RID-Protection region index:**

RID indicates the selected protection region. For example, 000 represents the 0<sup>th</sup> protection region.

### 3.2.12. MPU operation

### 3.2.12.1.MPU enable control

The 0<sup>th</sup> bit of CR<20, 0> is the MPU enable bit. Before MPU becomes valid, At least one region should be specified and the corresponding NX, S, AP bits should be set. In addition, The MPU enable instruction must be located at the place where the address is valid. In other words, the address should not be in MPU denied region. Otherwise, unpredictable results may occur.

### 3.2.12.2. Memory access handling

When MPU is enabled, MPU will check whether the current access address locates at the protection region:

If the address is not located in any region, the memory access will be stopped;

If the address is located in one or more of those regions, the access will be controlled by the highest indexed region which has been enabled. (The highest is 7 while the lowest is 0).

### 3.2.12.3. Memory access start address setting

CR<20, 0> defines the start address and size of 4/8 protection regions. The size of protection region must be a power of 2, ranging from 1KB to 4GB. And the start address must be aligned with the size of region. For example, the start address of an 8KB protection region could be 32'h12346000. However, for a 16KB protection region, this start address is not valid, instead 32'h12344000 could be a valid one.

# **C-Sky Confidential**

# 3.2.13. CPU Hint Register(CHR,CR<31,0>)

CR<31, 0> is used to implement all kinds of CPU hint operation in processor, which includes software reset and interrupt response acceleration.

|       | 31 16    | 6 | 15 | 5 | 4   | 3 | 0 |

|-------|----------|---|----|---|-----|---|---|

|       | SRST_VAL |   | 0  |   | IAE |   | 0 |

| Reset | 0        |   | 0  |   | 0   |   | 0 |

Chart 3-12 CPU hint register

### Software reset decision value SRST\_VAL:

If SRST\_VAL is written into a certain value, the software reset will be implemented. The default value is 16'hABCD.

The software reset operation will reset all general purpose registers, control registers. And a software reset identified signal lasting one system clock period will be sent outside by the processor.

If the processor executes software reset instruction under normal running mode, then it will enter the reset exception handling program (i.e. Exception handler with vector number 0) to execute corresponding operation; However, if the processor executes the instruction under debug mode, then the processor will remains at debug mode. Instead, it will automatically enter the exception handling program (i.e. Exception handler with vector number 0) to execute corresponding operation when exiting debug mode.

Any reading operation for SRST\_VAL will unconditionally returns 0, and writing value other than the specific one to the register will not produce any result.

The software reset operation above must be executed on the condition that the exception enable bit (EE bit in the PSR) has been set. Otherwise unrecoverable exception will occur.

### Interrupt response acceleration enable bit IAE:

When IAE equals 1, the interrupt response acceleration mechanism is enabled. The processor will push the current contents into stack speculatively which accelerates the interrupt response.

When IAE equals 0, the interrupt response acceleration mechanism is disabled.

The above interrupt response acceleration mechanism controlled by IAE bit is only valid when the interrupt nesting instructions NIE,NIR,IPUSH,IPOP are hardware configured.

# **C-Sky Confidential**

# 3.2.14. User mode stack pointer register

# 14(R14(user),CR<14,1>)

In the supervisor mode, R14(user) is mapped to the control register CR<14,1>. In other words, supervisor can access CR<14, 1> to control R14(user).

# **C-Sky Confidential**

# 4. 32-bit Instructions

This chapter mainly focus on the 32-bit instruction set of CSKY, including its functionality, coding and addressing mode.

# 4.1. Functional Classification of 32-bit Instructions

According to functions, 32 bit instructions of CSKY can be classified as following categories:

- Data operation instruction

- Branch jump instruction

- Memory access instruction

- Privileged instruction

- Special function instruction

# 4.1.1. Data Operation Instructions

Data operation instructions can be further classified as:

Add/Sub Instructions:

| ADDU32Unsigned-addADDC32Unsigned-add with carryADDI32Unsigned-add immediateSUBU32Unsigned-subSUBC32Unsigned-sub with carrySUBI32Unsigned-sub immediateRSUB32Reversed subIXH32Indexed half-word |        |                                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|--|--|

| ADDI32Unsigned-add immediateSUBU32Unsigned-subSUBC32Unsigned-sub with carrySUBI32Unsigned-sub immediateRSUB32Reversed sub                                                                      | ADDU32 | Unsigned-add                   |  |  |

| SUBU32Unsigned-subSUBC32Unsigned-sub with carrySUBI32Unsigned-sub immediateRSUB32Reversed sub                                                                                                  | ADDC32 | Unsigned-add with carry        |  |  |

| SUBC32Unsigned-sub with carrySUBI32Unsigned-sub immediateRSUB32Reversed sub                                                                                                                    | ADDI32 | Unsigned-add immediate         |  |  |

| SUBI32     Unsigned-sub immediate       RSUB32     Reversed sub                                                                                                                                | SUBU32 | Unsigned-sub                   |  |  |

| RSUB32 Reversed sub                                                                                                                                                                            | SUBC32 | Unsigned-sub with carry        |  |  |

|                                                                                                                                                                                                | SUBI32 | Unsigned-sub immediate         |  |  |

| IXH32 Indexed half-word                                                                                                                                                                        | RSUB32 | Reversed sub                   |  |  |

|                                                                                                                                                                                                | IXH32  | Indexed half-word              |  |  |

| IXW32 Indexed word                                                                                                                                                                             | IXW32  | Indexed word                   |  |  |

| INCF32 Add immediate with carry bit 0                                                                                                                                                          | INCF32 | Add immediate with carry bit 0 |  |  |

| INCT32 Add immediate with carry bit 1                                                                                                                                                          | INCT32 | Add immediate with carry bit 1 |  |  |

| DECF32 Sub immediate with carry bit 0                                                                                                                                                          | DECF32 | Sub immediate with carry bit 0 |  |  |

| DECT32 Sub immediate with carry bit 1                                                                                                                                                          | DECT32 | Sub immediate with carry bit 1 |  |  |

Chart 4-1 list of 32-bit Add/Sub Instructions

Logic Instructions:

### Chart 4-2 list of 32-bit Logic Instructions

| AND32   | Bitwise logic and            |

|---------|------------------------------|

| ANDI32  | Bitwise logic and immediate  |

| ANDN32  | Bitwise logic nand           |

| ANDNI32 | Bitwise logic nand immediate |

| OR32    | Bitwise logic or             |

# **C-Sky Confidential**

| ORI32  | Bitwise logic or immediate  |

|--------|-----------------------------|

| XOR32  | Bitwise logic xor           |

| XORI32 | Bitwise logic xor immediate |

| NOR32  | Bitwise logic nor           |

| NOT32  | Bitwise logic not           |

Shift instructions:

### Chart 4-3 list of 32-bit Shift Instructions

| LSL32   | Logic shift left                              |

|---------|-----------------------------------------------|

| LSLI32  | Logic shift left immediate                    |

| LSLC32  | Logic shift left immediate to carry bit       |

| LSR32   | Logic shift right                             |

| LSRI32  | Logic shift right immediate                   |

| LSRC32  | Logic shift right immediate to carry bit      |

| ASR32   | Arithmetic shift right                        |

| ASRI32  | Arithmetic shift right immediate              |

| ASRC32  | Arithmetic shift right immediate to carry bit |

| ROTL32  | Circular shift left                           |

| ROTLI32 | Circular shift left immediate                 |

| XSR32   | Extended shift right                          |

|         |                                               |

Comparison instructions:

### Chart 4-2 list of 32-bit comparison instructions

| CMPNEI32 | Not equal immediate               |

|----------|-----------------------------------|

| CMPHSI32 | Unsigned lager or equal immediate |

| CMPLTI32 | Signed smaller immediate          |

Data Transfer Instructions:

LRW32

# MOV32Data TransferMOVF32Data Transfer with carry bit 0MOVT32Data Transfer with carry bit 1MOVI32Data Transfer immediateMOVIH32High word data transfer immediateMVC32Carry bit data transfer

### Chart 4-3 list of 32-bit data transfer instructions

# **C-Sky Confidential**

Data transfer from memory

Bit instructions:

### Chart 4-4 list of 32-bit Bit instructions

| BCLRI32 | Clear immediate |

|---------|-----------------|

| BSETI32 | Set immediate   |

| BTSTI32 | Test immediate  |

Extract and Insert Instructions:

Chart 4-5 list of 32-bit Extract and Insert Instructions

| XTRB0.32 | Extract byte 0 and unsigned extend |

|----------|------------------------------------|

| XTRB1.32 | Extract byte 1 and unsigned extend |

| XTRB2.32 | Extract byte 2 and unsigned extend |

| XTRB3.32 | Extract byte 3 and unsigned extend |

Mul and Div Instructions:

Chart 4-6 list of 32-bit Mul and Div instruction

| MULT32 | Multiply |  |

|--------|----------|--|

|        |          |  |

Other Arithmetic Instructions:

Chart 4-7 list of other 32-bit arithmetic Instructions

| FF0. 32  | Fast find 0                   |

|----------|-------------------------------|

| FF1. 32  | Fast find 1                   |

| BMASKI32 | Bit mask generation immediate |

| BGENI32  | Bit generation immediate      |

# 4.1.2. Branch Jump Instructions

Branch jump instructions can be further classified as:

Branch instructions:

### Chart 4-8 list of 32-bit branch instructions

| BT32 | Branch instruction with carry bit 1 |

|------|-------------------------------------|

| BF32 | Branch instruction with carry bit 0 |

Jump instructions:

Chart 4-9 list of 32-bit jump instruction

| BR32  | Unconditional jump |

|-------|--------------------|

| BSR32 | Jump to Subprogram |

| RTS32 | Link register jump |

# **C-Sky Confidential**

# 4.1.3. Memory Access Instruction

Memory access instructions can be further classified as:

Immediate operand offset access instructions

Chart 4-10 List of 32-bit Immediate operand offset access instruction

| LD32.B  | Load unsigned and extended byte      |

|---------|--------------------------------------|

| LD32.BS | Load signed and extended byte        |

| LD32.H  | Load unsigned and extended half-word |

| LD32.HS | Load signed and extended half-word   |

| LD32.W  | Load word                            |

| ST32.B  | Store byte                           |

| ST32.H  | Store half-word                      |

| ST32.W  | Store word                           |

Multi-register access instructions:

Chart 4-13 List of 32-bit multi-register access instructions

| LDQ32 | Load consecutive quad word  |

|-------|-----------------------------|

| LDM32 | Load consecutive multiword  |

| STQ32 | Store consecutive quad word |

| STM32 | Store consecutive multiword |

# 4.1.4. Privileged Instruction

Privileged instruction can be further divided into:

Control register operation instructions:

Chart 4-14 List of 32-bit control register operation instructions

| MFCR32 | Read from control register |

|--------|----------------------------|

| MTCR32 | Write to control register  |

Low power consumption instructions:

Chart 4-11 List of 32-bit low power consumption instructions

|   | WAIT32 | Enter low power consumption wait mod  |

|---|--------|---------------------------------------|

|   | DOZE32 | Enter low power consumption doze mode |

| 4 | STOP32 | Enter low power consumption stop mode |

Abnormal return instruction:

### Chart 4-12 List of 32-bit abnormal return instructions C-Sky Confidential

0

RTE32

Return from exception/interrupt

# 4.1.5. Special Function Instructions

Special function includes

Chart 4-13 List of 32-bit Special function

| SYNC32 | Synchronize CPU                     |

|--------|-------------------------------------|

| TRAP32 | Unconditional operating system trap |

# 4.2. Encoding of 32-bit Instructions

The 32-bit instruction set of CSKY can be divided into 3 categories in coding style:

- Jump type (J type)

- Immediate operand type (I type)

- Register type (R type)

### 4.2.1. Jump type

The coding mode of jump type (J type) of 32-bit instructions is shown in the following chart:

313029 2625

| 1 1 | OP | Offset/User Define |

|-----|----|--------------------|

| 2   | 4  | 26                 |

OP field is the main operation code and instructions of this coding type can be identified through 4-bit operation code; Offset/User Define field is the offset of jump instruction or user defined reserved domain.

### 4.2.2. Immediate operand type

Immediate operand type (I type) of 32-bit instructions covers two coding modes including 16-bit immediate operand and 12-bit immediate operand.

The coding mode of 16-bit immediate operand is shown in the following chart:

| 3130 | 29 26 | 25 21  | 20 16 | 15    | 0 |

|------|-------|--------|-------|-------|---|

| 11   | OP    | RZ/SOP | RX    | IMM16 |   |

| 2    | 4     | 5      | 5     | 16    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 4-bit main operation code; RZ/SOP field is the destination register field or sub-operation code field; RX field is the first source register; IMM16 field is the 16-bit immediate operand.

# **C-Sky Confidential**

The coding mode of 12-bit immediate operand is shown in the following chart:

| 3130 | 29 26 | 25 21 | 20 16 | 15 12 | 11 0  |

|------|-------|-------|-------|-------|-------|

| 11   | OP    | RZ/RY | RX    | SOP   | IMM12 |

| 2    | 4     | 5     | 5     | 4     | 12    |

OP field is the main operation code and the instruction or instruction type can be identified through 4-bit main operation code; RZ/RY field is the destination register field or second source register field; RX field is the first source register; SOP field is the sub-operation code field; IMM12 field is the 12-bit immediate operand. The instruction type can be gained after decoding the main operation code OP, and the specific instruction can be obtained only after further decoding the sub-operation code SOP.

### 4.2.3. Register Type

The coding mode of register type (R type) of 32-bit instructions is shown in the following chart:

| 31302 | 29 26 | 25 21   | 20 16 | 15  | 10 9 5 | 4 0 |

|-------|-------|---------|-------|-----|--------|-----|

| 11    | OP    | RY/IMM5 | RX    | SOP | Pcode  | RZ  |

| 2     | 4     | 5       | 5     | 6   | 5      | 5   |

OP field is the main operation code and the instruction type can be identified through 4-bit main operation code; RY/IMM5 field is the second source register field or 5-bit immediate operand; RX is the first source register; SOP field is the sub-operation code field; Pcode is the parallel operation code field; RZ field is the destination register field. As for some instructions, the instruction type is gained after decoding the main operation code SOP, and then the specific instruction is identified by decoding the parallel operation code Pcode which adopts one-hot coding mode.

# 4.3. Operand Addressing Mode of 32-bit Instructions

The 32-bit instruction set of CSKY follows three instruction coding modes and each has its own operand addressing mode. In the following context, all of the operand addressing modes will be introduced.

# 4.3.1. Addressing Mode of Jump-type Instructions

The 32-bit instructions of jump type in CSKY v2 only have one addressing mode.

### 4.3.1.1. Addressing Mode of 26-bit Immediate Operand

In the instructions that adopt the addressing mode of 26-bit immediate operand, there

# **C-Sky Confidential**

is an immediate operand field with the length of 26 bits. This field is considered as offset which can be used to generate destination address. Instruction of this format includes bsr32.

| 3130 | 29 26 | 25 0   |

|------|-------|--------|

| 11   | OP    | Offset |

| 2    | 4     | 26     |

### 4.3.2. Addressing Mode of Immediate Operand-type Instructions

The 32-bit instructions of immediate operand type in CSKY V2 have four addressing modes

### 4.3.2.1. Addressing Mode of Two Register 16-bit Immediate Operand

In the instructions that adopt the addressing mode of two register 16-bit immediate operand, the two register fields RX and RZ are source register field and destination register field; IMM16 field directly participates in data operation as 16-bit immediate operand. Instruction of this format includes ori32.

| 3130 | 29 26 | 25 21 | 20 16 | 15 0  |

|------|-------|-------|-------|-------|

| 11   | OP    | RZ    | RX    | IMM16 |

| 2    | 4     | 5     | 5     | 16    |

### 4.3.2.2. Addressing Mode of Single Register 16-bit Immediate Operand

The instructions that adopt the addressing mode of single register 16-bit immediate operand have two formats.

In the first format, SOP field is the sub-operation code field; RX field is the source register field; IMM16 field directly participate in data operation as 16-bit immediate operand. Instructions of this format include cmphsi32, cmplti32.

| 3130 | 29 26 | 25  | 2120 16 | 15 0  |

|------|-------|-----|---------|-------|

| 11   | OP    | SOP | RX      | IMM16 |

| 2    | 4     | 5   | 5       | 16    |

In the second format, SOP field is the sub-operation code field; RZ field is the destination register field; IMM16 field can either be used in data operation as 16-bit immediate operand or be left to user for customization. Instructions of this format include movi32, movih32 and Irw32.

| 313029 | 2625 | 2120 | 1615 | 0 |

|--------|------|------|------|---|

|--------|------|------|------|---|

# **C-Sky Confidential**

|    |    | [   | [  | 33    |

|----|----|-----|----|-------|

| 11 | OP | SOP | RZ | IMM16 |

| 2  | 4  | 5   | 5  | 16    |

### 4.3.2.3. Addressing Mode of 16-bit Immediate Operand

In the instructions that adopt the addressing mode of 16-bit immediate operand, there is an immediate operand field with the length of 16 bits which is considered as offset and can be used to generate destination address. Instructions of this format include br32, bf32, bt32.

|   | 313029 | 9 26 | 25 21 | 20 16 | 15    | 0 |

|---|--------|------|-------|-------|-------|---|

|   | 11     | OP   | SOP   | 00000 | IMM16 |   |

| - | 2      | 4    | 5     | 5     | 16    |   |

### 4.3.2.4. Addressing Mode of Two Registers 12-bit Immediate Operand

In the instructions that adopt the addressing mode of two registers 12-bit immediate operand, RZ field is the destination register field or second source register field; RX field is the first source register field; SOP field is the sub-operation code field; IMM12 field can be used to generate destination address as 12-bit relative offset. Instructions of this format include Id32.b, Id32.h, Id32.w, Id32.bs, Id32.hs, st32.b, st32.h, addi32, subi32, andi32, andni32 and xori32.

| 313 | 029 2 | 625 21 | 20 16 | 15 12 | 211 |       | 0 |

|-----|-------|--------|-------|-------|-----|-------|---|

| 1 1 | OP    | RZ     | RX    | SOP   |     | IMM12 |   |

| 2   | 4     | 5      | 5     | 4     |     | 12    |   |

### 4.3.3. Addressing Mode of Register-type Instructions

The 32-bit instructions of register type in CSKY V2 have five addressing modes.

### 4.3.3.1. Addressing Mode of Ternary Registers

In addressing mode of ternary register, RY is the second source register field; RX field is the first source register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field; RZ is the destination register field. Instructions of this format include addu32, addc32, subu32, subc32, ixh32, ixw32, and32, andn32, or32, xor32, nor32, lsl32, lsr32, asr32, rotl32, mult32.

### 4.3.3.2. Addressing Mode of Two Register 5-bit Immediate Operand

Addressing mode of two register 5-bit immediate operand can be further divided into two formats.

In the first format, IMM5 field is the 5-bit immediate operand and treated as source operand; RX field is the source register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field; RZ field is the destination register field. Instructions of this format include Isli32、Isri32、asri32、rotli32、Islc32、Islc32、asrc32、xsr32、bclri32、bseti32.

| 31302 | 29 26 | 25 21 | 20 16 | 615 10 | 9 5   | 4 ( | 0 |

|-------|-------|-------|-------|--------|-------|-----|---|

| 11    | OP    | IMM5  | RX    | SOP    | Pcode | RZ  |   |

| 2     | 4     | 5     | 5     | 6      | 5     | 5   |   |

In the second format, IMM5 field is the 5-bit immediate operand and used as source operand; RX field is the source register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field; RZ field is the destination register field or second source register field. Instructions of this format include incf32, inct32, decf32, decf32.

| 3130 | 29 26 | 25 2 <sup>-</sup> | 120 16 | 615 10 | )95   | 4 0  |

|------|-------|-------------------|--------|--------|-------|------|

| 11   | OP    | RZ                | RX     | SOP    | Pcode | IMM5 |

| 2    | 4     | 5                 | 5      | 6      | 5     | 5    |

### 4.3.3.3. Addressing Mode of Two Register

In the format, RZ field is the destination register field; RX field is the source register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field. Instructions of this format include xtrb0.32、xtrb1.32、xtrb2.32、xtrb3.32、ff0.32、ff1.32.

| 3130 | 29 2 | 625 | 2120 |    | 1615 | 10  | 9 5   | 4  | 0 |

|------|------|-----|------|----|------|-----|-------|----|---|

| 11   | OP   | 0   |      | RX |      | SOP | Pcode | RZ |   |

| 2    | 4    | 5   |      | 5  |      | 6   | 5     | 5  |   |

### 4.3.3.4. Addressing Mode of Single Register 5-bit Immediate Operand

Instructions that adopt the addressing mode of single register 5-bit immediate operand can be further divided into two formats

In the first format, IMM5 field is the 5-bit immediate operand and treated as source operand; RX field is the source register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field. Instruction of this format includes btsti32.

# **C-Sky Confidential**

| 3130 | 29 26 | 625 21 | 20 16 | 15 1 | 0 9 5 | 4 0 |

|------|-------|--------|-------|------|-------|-----|

| 11   | OP    | IMM5   | RX    | SOP  | Pcode | 0   |

| 2    | 4     | 5      | 5     | 6    | 5     | 5   |

In the second format, IMM5 field is the 5-bit immediate operand and treated as source operand; SOP field is the sub-operation code field; Pcode is the parallel operation code field; RZ field is the destination register field. Instruction of this format includes bmaski32.

| 313 | 029  | 26 | 25   | 21 20 | 1 | 615 | 10  | 9     | 54 |    | 0 |

|-----|------|----|------|-------|---|-----|-----|-------|----|----|---|

| 1 ' | I OP | )  | IMM5 |       | 0 |     | SOP | Pcode | •  | RZ |   |

| 2   | 4    |    | 5    |       | 5 |     | 6   | 5     |    | 5  |   |

### 4.3.3.5. Addressing Mode of Single Register

RZ is the destination register field; SOP field is the sub-operation code field; Pcode is the parallel operation code field. Instructions of this format include mvc32.

| 3130 | 29 26 | 25 21 | 20 16 | 15 10 | 9 5   | 4  | 0 |

|------|-------|-------|-------|-------|-------|----|---|

| 11   | OP    | 0     | 0     | SOP   | Pcode | RZ |   |

| 2    | 4     | 5     | 5     | 6     | 5     | 5  |   |

# **C-Sky Confidential**

## 5. 16-bit Instruction Set

In this chapter, 16-bit instruction set of CSKY will be introduced, covering its functional classification, encoding and addressing mode.

## 5.1. Functional Classification of 16-bit Instructions

According to functions of instruction realization the 16-bit instruction set can be classified into following categories:

- Data operation instruction

- Branch jump instruction

- Memory access instruction

### 5.1.1. Data Operation Instruction

Data operation instruction can be further divided into:

Add/Sub instruction:

| ADDU16 | Add unsigned            |

|--------|-------------------------|

| ADDC16 | Add unsigned with carry |

| ADDI16 | Add unsigned immediate  |

| SUBU16 | Sub unsigned            |

| SUBC16 | Sub unsigned with carry |

| SUBI16 | Sub unsigned immediate  |

|        |                         |

Chart 5-1 List of 16-bit Add/Sub instructions

Logical operation instruction:

| AND16  | Bitwise logical and     |

|--------|-------------------------|

| ANDN16 | Bitwise logical and-not |

| OR16   | Bitwise logical or      |

| XOR16  | Bitwise logical xor     |

| NOR16  | Bitwise logical or-not  |

| NOT16  | Bitwise logical not     |

Chart 5-2 List of 16-bit Logical operation instructions

#### Shift instruction:

| 1000 |        |                               |

|------|--------|-------------------------------|

|      | LSL16  | Logical shift left            |

|      | LSLI16 | Logical shift left immediate  |

|      | LSR16  | Logical shift right           |

|      | LSRI16 | Logical shift right immediate |

|      | ASR16  | Arithmetic shift right        |

|      |        |                               |

# **C-Sky Confidential**

| ASRI16 | Arithmetic shift right immediate |

|--------|----------------------------------|

| ROTL16 | Rotate left                      |

Chart 5-3 List of 16-bit Shift instructions

#### Compare instruction:

| CMPNE16   | Compare unequal                          |

|-----------|------------------------------------------|

| CMPNEI16  | Compare unequal immediate                |

| CMPHS16   | Compare unsigned when greater or equal   |

| CMPHSI16  | Compare immediate unsigned when          |

| CIMPHSING | greater or equal                         |

| CMPLT16   | Compare signed when smaller              |

| CMPLTI16  | Compare immediate signed when smaller    |

| TST16     | Null-test                                |

| TSTNBZ16  | Register test without byte equal to zero |

Chart 5-4 List of 16-bit compare instructions

Data transfer instruction:

| MOV16  | Move                    |

|--------|-------------------------|

| MOVI16 | Move immediate          |

| MVCV16 | Carry bit data transfer |

| LRW16  | Read from memory        |

Chart 5-5 List of 16-bit data transfer instructions

Bit operation instruction:

| BCLRI16 | Bit clear immediate |

|---------|---------------------|

| BSETI16 | Bit set immediate   |

| BTSTI16 | Bit test immediate  |

Chart 5-6 List of 16-bit bit operation instructions

#### Extract and insert instruction:

| ZEXTB16 | Extract byte and extend unsigned      |

|---------|---------------------------------------|

| ZEXTH16 | Extract half-word and extend unsigned |

| SEXTB16 | Extract byte and extend signed        |

| SEXTH16 | Extract half-word and extend signed   |

| REVB16  | Extract half-word and extend signed   |

| REVH16  | Half-word byte-reverse                |

Chart 5-7 List of 16-bit extract and insert instructions

# **C-Sky Confidential**

Multiply-divide instruction:

MULT16 Multiply

Chart 5-8 List of 16-bit multiply-divide instructions

### 5.1.2. Branch Jump Instruction

Branch jump instruction can be further divided into:

Branch instruction:

| BT16 | C=1 branch instruction |

|------|------------------------|

| BF16 | C=0 branch instruction |

Chart 5-9 List of 16-bit branch instructions

Jump instruction:

| BR16  | Unconditional jump          |

|-------|-----------------------------|

| JMP16 | Register jump               |

| JSR16 | Register jump to subprogram |

| RTS16 | Link register jump          |

Chart 5-9 List of 16-bit jump instructions

### 5.1.3. Memory Access Instruction

Memory access instruction can be further divided into:

Immediate operand offset access instruction:

| LD16.B | Load unsigned and extended byte      |

|--------|--------------------------------------|

| LD16.H | Load unsigned and extended half-word |

| LD16.W | Load word                            |

| ST16.B | Store byte                           |

| ST16.H | Store half-word                      |

| ST16.W | Store word                           |

Chart 5-10 List of 16-bit immediate operand offset access instructions

Multi-register access instructions:

|   | POP16   | Рор                      |

|---|---------|--------------------------|

|   | IPOP16  | Interrupt pop            |

| 1 | PUSH16  | Push                     |

|   | IPUSH16 | Interrupt push           |

|   | NIE16   | Interrupt nesting enable |

|   | NIR16   | Interrupt nesting return |

Chart 5-11 List of 16-bit Multi-register access instruction

# **C-Sky Confidential**

note: NIE16 and NIR16 need to be executed in supervisor mode

### 5.1.4. Privilege Instructions

16-bit Privilege instructions :

| NIE16 | Interrupt nesting enable |

|-------|--------------------------|

| NIR16 | Interrupt nesting return |

Chart 5-12 List of 16-bit Privilege instructions

note: NIE16 和 NIR16 are Multi-register access instructions at the same time.

### 5.2. Coding Mode of 16-bit Instructions

The 16-bit instruction set of CSKY V2 is almost consistent with the subset of 32-bit

instructions in coding style and it can be divided into three categories:

- Jump type (J type)

- Immediate operand type (I type)

- Register type (R type)

#### 5.2.1. Jump Type

The coding mode of jump type (J type) is shown in the following chart:

| 1514 | 13 10 | 9 0    |

|------|-------|--------|

| 0 0  | OP    | Offset |

| 2    | 4     | 10     |

OP field is the main operation code and instructions of this coding type can be identified through 4-bit main operation code; Offset field is the offset of jump instruction.

#### 5.2.2. Immediate Operand Type

Immediate operand type (I type) covers four coding modes including 3-bit immediate operand, 5-bit immediate operand, 7-bit immediate operand, and 8-bit immediate operand.

The coding mode of 3-bit immediate operand is shown in the following chart:

| 1514 | 13 11 | 10 8 | 7 5 | 4 2  | 1 0 |  |

|------|-------|------|-----|------|-----|--|

| 01   | OP    | RX   | RZ  | IMM3 | SOP |  |

| 2    | 3     | 3    | 3   | 3    | 2   |  |

OP field is the main operation code and the instruction or instruction type can be identified through 3-bit main operation code; RZ field is the destination register field; IMM3 field is the 3-bit immediate operand; SOP field is the sub-operation code field. The

# **C-Sky Confidential**

instruction type can be gained after decoding the main operation code OP, and the specific instruction can be obtained only after further decoding the sub-operation code SOP.

The coding mode of 5-bit immediate operand has three formats and the first format is shown in the following chart:

| 1514 | 13 11 | 10 8 | 7 5 | 4    | 0 |

|------|-------|------|-----|------|---|

| 0 1  | OP    | RX   | RZ  | IMM5 |   |

| 2    | 3     | 3    | 3   | 5    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 3-bit main operation code; RX field is the source register field; RZ field is the destination register field; IMM5 field is the 5-bit immediate operand

The second coding mode of 5-bit immediate operand is shown in the following chart:

| 1514 | 13 11 | 10 8 | 7 5 | 4    | 0 |

|------|-------|------|-----|------|---|

| 0 0  | OP    | RX   | SOP | IMM5 |   |

| 2    | 3     | 3    | 3   | 5    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 3-bit main operation code; RX field is the source register field; SOP field is the sub-operation code field; IMM5 field is the 5-bit immediate operand. The instruction type can be gained after decoding the main operation code OP, and the specific instruction can be obtained only after further decoding the sub-operation code SOP

The third coding mode of 5-bit immediate operand is shown in the following chart:

| 1514 | 13 11 | 10 8 | 7 5 | 4    | 0 |

|------|-------|------|-----|------|---|

| 10   | OP    | RX   | RZ  | IMM5 |   |

| 2    | 3     | 3    | 3   | 5    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 3-bit main operation code; RX field is the source register field; RZ field is the destination register field; IMM5 field is the 5-bit immediate operand.

The coding mode of 7-bit immediate operand is shown in the following chart:

| 1514 | 13 |    | 10 | 98   | 7   | 5   | 4 |      | 0 |

|------|----|----|----|------|-----|-----|---|------|---|

| 00   |    | OP |    | IMM2 | SOP | /RZ |   | IMM5 |   |

| 2    |    | 4  |    | 2    | 3   |     |   | 5    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 4-bit main operation code; IMM2 field and IMM5 field are two high bits

## **C-Sky Confidential**

and five low bits of 7-bit immediate operand; SOP/RZ field is the sub-operation code field or destination register field. The instruction type can be gained after decoding the main operation code OP, and the specific instruction can be obtained only after further decoding the sub-operation code SOP.

The coding mode of 8-bit immediate operand has two formats and the first format is shown in the following chart:

| 1514 | 13 11 | 10 8  | 7    | 0 |

|------|-------|-------|------|---|

| 0 0  | OP    | RX/RZ | IMM8 |   |

| 2    | 3     | 3     | 8    |   |

OP field is the main operation code and the instruction or instruction type can be identified through 3-bit main operation code; RZ/RX field is the destination register field or source register field; IMM8 field is the 8-bit immediate operand.

The second coding mode of 8-bit immediate operand is shown in the following chart: